No. 2022-1906

## UNITED STATES COURT OF APPEALS FOR THE FEDERAL CIRCUIT

VLSI TECHNOLOGY LLC,

Plaintiff-Appellee,

v.

INTEL CORPORATION,

Defendant-Appellant.

On Appeal from the United States District Court for the Western District of Texas in Case No. 6:21-cv-00057-ADA, Judge Alan D. Albright

#### NON-CONFIDENTIAL BRIEF FOR DEFENDANT-APPELLANT INTEL CORPORATION

AMANDA L. MAJOR

STEVEN J. HORN

WILMER CUTLER PICKERING

HALE AND DORR LLP

1875 Pennsylvania Avenue, NW

Washington, DC 20006

(202) 663-6000

MARY V. SOOTER WILMER CUTLER PICKERING HALE AND DORR LLP 1225 17th Street, Suite 2600 Denver, CO 80202 (720) 274-3135

September 14, 2022

WILLIAM F. LEE JOSEPH J. MUELLER LAUREN B. FLETCHER BENJAMIN N. ERNST ALISON BURTON WILMER CUTLER PICKERING HALE AND DORR LLP 60 State Street Boston, MA 02109 (617) 526-6000 William.Lee@wilmerhale.com

Attorneys for Defendant-Appellant Intel Corporation

#### PATENT CLAIMS AT ISSUE

#### Claim 1 of the '373 Patent

1. A method, comprising:

providing an integrated circuit with a memory;

operating the memory with an operating voltage;

determining a value of a minimum operating voltage of the memory;

providing a non-volatile memory (NVM) location;

- storing the value of the minimum operating voltage of the memory in the NVM location;

- providing a functional circuit on the integrated circuit exclusive of the memory;

- providing a first regulated voltage to the functional circuit;

- providing a second regulated voltage, the second regulated voltage is greater than the first regulated voltage;

- providing the first regulated voltage as the operating voltage of the memory when the first regulated voltage is at least the value of the minimum operating voltage; and

- providing the second regulated voltage as the operating voltage of the memory when the first regulated voltage is less than the value of the minimum operating voltage, wherein while the second regulated voltage is provided as the operating voltage of the memory, the first regulated voltage is provided to the functional circuit.

Appx111(13:7-28).

#### Claim 14 of the '759 Patent

14. A system comprising:

a bus capable of operation at a variable clock frequency;

a first master device coupled to the bus, the first master device configured to provide a request to change a clock frequency of a highspeed clock in response to a pre-defined change in performance of the first master device, wherein the predefined change in performance is due to loading of the first master device as measured within a predefined time interval; and

a programmable clock controller having an embedded computer program therein, the computer program including instructions to:

receive the request provided by the first master device;

provide the clock frequency of the high-speed clock as an output to control a clock frequency of a second master device coupled to the bus in response to receiving the request provided by the first master device; and

provide the clock frequency of the high-speed clock as an output to control the variable clock frequency of the bus in response to receiving the request provided by the first master device.

Appx123-124(8:50-9:4).

## **CERTIFICATE OF INTEREST**

Counsel for Defendant-Appellant Intel Corporation certifies the following:

**1. Represented Entities**. Fed. Cir. R. 47.4(a)(1). Provide the full names of all entities represented by undersigned counsel in this case.

Intel Corporation.

**2. Real Party in Interest**. Fed. Cir. R. 47.4(a)(2). Provide the full names of all real parties in interest for the entities. Do not list the real parties if they are the same as the entities.

None.

3. Parent Corporations and Stockholders. Fed. Cir. R. 47.4(a)(3). Provide the full names of all parent corporations for the entities and all publicly held companies that own 10% or more stock in the entities.

None.

4. Legal Representatives. List all law firms, partners, and associates that (a) appeared for the entities in the originating court or agency or (b) are expected to appear in this court for the entities. Do not include those who have already entered an appearance in this court. Fed. Cir. R. 47.4(a)(4).

WILMER CUTLER PICKERING HALE AND DORR LLP: Arthur W. Coviello, Jeffrey A. Dennhardt, Felicia H. Ellsworth, Jordan L. Hirsch, Thomas Lampert, Gregory H. Lantier, James M. Lyons, George F. Manley, Alexis Pfeiffer, Kate Saxton, Joshua L. Stern, Louis W. Tompros, Anh-Khoa Tran, Paul T. Vanderslice

KELLY HART & HALLMAN LLP: J. Stephen Ravel, Kelly Ransom, Sven Stricker (former)

PILLSBURY WINTHROP SHAW PITTMAN LLP: Brian C. Nash (former)

KIRKLAND & ELLIS LLP: John C. O'Quinn

James Eric Wren, III

5. Related Cases. Provide the case titles and numbers of any case known to be pending in this court or any other court or agency that will directly affect or be directly affected by this court's decision in the pending appeal. Do not include the originating case number(s) for this case. Fed. Cir. R. 47.4(a)(5). See also Fed. Cir. R. 47.5(b).

*VLSI Technology LLC v. Intel Corp.*, No. 6:21-cv-00299-ADA (W.D. Tex.) (formerly No. 6:19-cv-00255-ADA);

*VLSI Technology LLC v. Intel Corp.*, No. 6:19-cv-00977-ADA (W.D. Tex.) (formerly No. 6:19-cv-256-ADA);

VLSI Technology LLC v. Intel Corp., No. 1:18-cv-966-CFC (D. Del.);

VLSI Technology LLC v. Intel Corp., No. 5:17-cv-05671-BLF (N.D. Cal.);

Intel Corp. v. Fortress Investment Group, No. 2021-0021-MTZ (Del. Ch.);

OpenSky Industries, LLC v. VLSI Technology LLC, IPR2021-01064 (PTAB);

Patent Quality Assurance, LLC v. VLSI Technology LLC, IPR2021-01229 (PTAB);

Intel Corp. v. VLSI Technology LLC, IPR2022-00366 (PTAB) (joined with IPR2021-01064);

Intel Corp. v. VLSI Technology LLC, IPR2022-00479 (PTAB) (joined with IPR2021-01229).

6. Organizational Victims and Bankruptcy Cases. Provide any information required under Fed. R. App. P. 26.1(b) (organizational victims in criminal cases) and 26.1(c) (bankruptcy case debtors and trustees). Fed. Cir. R. 47.4(a)(6).

None.

Dated: September 14, 2022

/s/ William F. Lee

WILLIAM F. LEE WILMER CUTLER PICKERING HALE AND DORR LLP 60 State Street Boston, MA 02109 (617) 526-6000

## TABLE OF CONTENTS

|          |       | Page                                 |

|----------|-------|--------------------------------------|

| PATENT C | CLAIN | IS AT ISSUE                          |

| CERTIFIC | ATE C | DF INTERESTi                         |

| TABLE O  | F AUT | HORITIES viii                        |

| STATEME  | ENT O | F RELATED CASES1                     |

| JURISDIC | TIONA | AL STATEMENT2                        |

| INTRODU  | CTIO  | N3                                   |

| STATEME  | ENT O | F ISSUES5                            |

| STATEME  | ENT O | F FACTS6                             |

| A.       | VLS   | I's Serial Lawsuits Against Intel6   |

| B.       | VLS   | I's Assertion Of The '373 Patent7    |

|          | 1.    | The '373 patent7                     |

|          | 2.    | Intel's accused C6SRAM multiplexer10 |

| C.       | VLS   | I's Assertion Of The '759 Patent12   |

|          | 1.    | The '759 patent12                    |

|          | 2.    | Intel's accused SpeedShift feature14 |

| D.       | Intel | 's License Defense15                 |

| E.       | Trial |                                      |

|          | 1.    | Fortress evidence16                  |

|          | 2.    | VLSI's infringement case16           |

|          | 3.    | Damages evidence17                   |

|      |      | 4.     | Verdict                                                                                     | 20 |

|------|------|--------|---------------------------------------------------------------------------------------------|----|

|      | F.   | Post-  | Trial Proceedings                                                                           | 21 |

|      |      | 1.     | Intel's juror misconduct motion                                                             | 21 |

|      |      | 2.     | Intel's other post-trial motions                                                            | 22 |

|      |      | 3.     | Intel's license defense                                                                     | 22 |

|      |      | 4.     | Final judgment                                                                              | 22 |

| SUM  | IMAR | Y OF 2 | ARGUMENT                                                                                    | 23 |

| ARG  | UMEN | NT     |                                                                                             | 25 |

| I.   | STAN | DARD   | OF REVIEW                                                                                   | 25 |

| II.  |      |        | GEMENT JUDGMENT FOR THE '373 PATENT SHOULD BE                                               | 26 |

|      | A.   |        | 's Products Do Not Store The Claimed "Minimum rating Voltage."                              | 26 |

|      | B.   |        | 's Products Do Not Provide The First And Second<br>lated Voltages "When" The Claims Require | 33 |

| III. |      |        | GEMENT JUDGMENT FOR THE '759 PATENT SHOULD BE                                               | 37 |

|      | A.   |        | ecution History Estoppel Bars VLSI's Equivalents ory                                        |    |

|      | B.   |        | Jury's Infringement Finding Is Unsupported By<br>tantial Evidence.                          | 42 |

| IV.  |      |        | CT COURT ERRONEOUSLY AND PREJUDICIALLY<br>VLSI TO INTRODUCE <i>NONCOMPARABLE</i> AGREEMENTS | 46 |

|      | A.   |        | I's Expert Agreed The Intel Agreements Were <i>Not</i> parable To The Hypothetical License. | 46 |

|     | В.                                                                                    | Nonce                                                                                           | District Court's Rationale For Allowing The omparable Agreements Does Not Justify Their ssion.    | 48 |

|-----|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----|

|     | C.                                                                                    | Agree                                                                                           | Erroneous Admission Of The Noncomparable<br>ements Requires A New Trial On Liability And<br>ages. | 53 |

| V.  | VLSI'S DAMAGES MODEL SHOULD HAVE BEEN EXCLUDED AND<br>Cannot Support The Jury's Award |                                                                                                 | 54                                                                                                |    |

|     | A.                                                                                    | Dr. Sullivan's Regression Analysis Was Not Tied To The<br>Accused Products And Features         |                                                                                                   |    |

|     | В.                                                                                    | Dr. Sullivan Used Unreliable Inputs From VLSI's Technical Experts.                              |                                                                                                   | 59 |

|     |                                                                                       | 1.                                                                                              | Dr. Annavaram's '373-related tests used non-<br>accused products and features                     | 59 |

|     |                                                                                       | 2.                                                                                              | Dr. Annavaram's '759-related tests included benefits not attributable to the patented feature     | 61 |

|     | C.                                                                                    | VLSI                                                                                            | Improperly Sought Disgorgement Of Intel's Profits                                                 | 62 |

|     | D.                                                                                    | VLSI's Introduction Of Intel's Total Accused Revenues<br>Violated The Entire Market Value Rule. |                                                                                                   |    |

| VI. | THE DISTRICT COURT ERRONEOUSLY DENIED INTEL'S MOTION TO<br>ADD A LICENSE DEFENSE      |                                                                                                 |                                                                                                   | 66 |

|     | A.                                                                                    | Intel's Motion Was Timely6                                                                      |                                                                                                   |    |

|     | B.                                                                                    | Intel's                                                                                         | s Amendment Was Not Futile                                                                        | 67 |

|     | C.                                                                                    |                                                                                                 | Prejudice To Intel In Not Allowing Amendment Is me.                                               | 71 |

| CON | CLUSI                                                                                 | ON                                                                                              |                                                                                                   | 72 |

ADDENDUM

## CERTIFICATE OF SERVICE

### CERTIFICATE OF COMPLIANCE

## CONFIDENTIAL MATERIAL OMITTED

The material omitted from pages 19, 20, 46, and 52 contains confidential Intel and third-party settlement/licensing information; the material omitted from page 21 contains confidential information regarding a juror; and the material omitted from page 64 contains confidential Intel financial information. The material omitted from Addendum pages Appx3-4 contains confidential Intel and third-party licensing information and confidential material regarding VLSI's CEO from a district court order filed under seal; the material omitted from Addendum pages Appx24, Appx43-46, Appx48, Appx55, Appx63-64, Appx77-78, Appx82-83, and Appx85-90 contains confidential Intel technical information from district court orders filed under seal; and the material omitted from Addendum pages Appx96-97 contains confidential Intel financial information from a district court order seal.

## **TABLE OF AUTHORITIES**

## CASES

| 5 |

|---|

| 3 |

| 0 |

| 1 |

| 8 |

| 3 |

| 7 |

| 3 |

| 8 |

| 4 |

| 6 |

| 1 |

|   |

| Daubert v. Merrell Dow Pharmaceuticals, Inc.,<br>509 U.S. 579 (1993)                                                      | 4 |

|---------------------------------------------------------------------------------------------------------------------------|---|

| Deering Precision Instruments, L.L.C. v. Vector Distribution Systems, Inc.,<br>347 F.3d 1314 (Fed. Cir. 2003) 40-41       | 1 |

| <i>Dodge v. Cotter Corp.</i> ,<br>328 F.3d 1212 (10th Cir. 2003)49                                                        | 9 |

| Elbit Systems Land & C4I Ltd. v. Hughes Network Systems, LLC,<br>927 F.3d 1292 (Fed. Cir. 2019)                           | 7 |

| <i>Ethicon Endo-Surgery, Inc. v. United States Surgical Corp.</i> ,<br>149 F.3d 1309 (Fed. Cir. 1998)45                   | 5 |

| <i>Festo Corp. v. Shoketsu Kinzoku Kogyo Kabushiki Co.</i> , 344 F.3d 1359 (Fed. Cir. 2003) (en banc)40                   | 0 |

| Festo Corp. v. Shoketsu Kinzoku Kogyo Kabushiki Co.,<br>493 F.3d 1368 (Fed. Cir. 2007)                                    | 5 |

| <i>Finalrod IP, LLC v. John Crane, Inc.</i> ,<br>838 F. App'x 562 (Fed. Cir. 2021) (nonprecedential)                      | 4 |

| <i>Finjan, Inc. v. Blue Coat Systems, Inc.,</i><br>879 F.3d 1299 (Fed. Cir. 2018)                                         | 5 |

| Gasoline Products Co. v. Champlin Refining Co.,<br>283 U.S. 494 (1931)                                                    | 4 |

| <i>Giles v. General Electric Co.</i> ,<br>245 F.3d 474 (5th Cir. 2001)                                                    | 4 |

| <i>Guile v. United States</i> ,<br>422 F.3d 221 (5th Cir. 2005)                                                           | 3 |

| Highmark Inc. v. Allcare Health Management System, Inc.,<br>572 U.S. 559 (2014)                                           | 5 |

| Huawei Technologies Co. v. T-Mobile US, Inc.,<br>No. 2:16-CV-00052-JRG-RSP, 2017 WL 7052466 (E.D. Tex.<br>Sept. 10, 2017) | 8 |

| <b>i</b> , , ,                                                                                                            |   |

| Oyster Optics, LLC v. Infinera Corp.,<br>843 F. App'x 298 (Fed. Cir. 2021) (nonprecedential)                                           |

|----------------------------------------------------------------------------------------------------------------------------------------|

| <i>Pharma Tech Solutions, Inc. v. LifeScan, Inc.</i> ,<br>942 F.3d 1372 (Fed. Cir. 2019)                                               |

| <ul><li>Philips Electronics North America Corp. v. Contec Corp.,</li><li>177 F. App'x 981 (Fed. Cir. 2006) (nonprecedential)</li></ul> |

| Pioneer Magnetics, Inc. v. Micro Linear Corp.,<br>330 F.3d 1352 (Fed. Cir. 2003)                                                       |

| Power Integrations, Inc. v. Fairchild Semiconductor International, Inc.,<br>711 F.3d 1348 (Fed. Cir. 2013)                             |

| Power Integrations, Inc. v. Fairchild Semiconductor International, Inc.,<br>904 F.3d 965 (Fed. Cir. 2018)                              |

| <i>ResQNet.com, Inc. v. Lansa, Inc.</i> , 594 F.3d 860 (Fed. Cir. 2010)                                                                |

| <i>Retractable Technologies Inc. v. Becton Dickinson &amp; Co.</i> ,<br>No. 2:07-CV-250, 2009 WL 8725107 (E.D. Tex. Oct. 8, 2009)53    |

| <i>Rodriguez. v. Riddell Sports, Inc.</i> ,<br>242 F.3d 567 (5th Cir. 2001)                                                            |

| <i>Rude v. Westcott</i> ,<br>130 U.S. 152 (1889)                                                                                       |

| Sage Products, Inc. v. Devon Industries, Inc.,<br>126 F.3d 1420 (Fed. Cir. 1997)                                                       |

| Searfoss v. Pioneer Consolidated Corp.,<br>374 F.3d 1142 (Fed. Cir. 2004)                                                              |

| <i>Sheehan v. AssuredPartners, Inc.</i> ,<br>C.A. No. 2019-0333-AML, 2020 WL 2838575 (Del. Ch. May 29, 2020)70                         |

| St. Clair Intellectual Property Consultants, Inc. v. Acer, Inc.,<br>935 F. Supp. 2d 779 (D. Del. 2013)                                 |

| <i>Stragent, LLC v. Intel Corp.</i> ,<br>No. 6:11-cv-421, 2014 WL 12611339 (E.D. Tex. Mar. 12, 2014)56    |

|-----------------------------------------------------------------------------------------------------------|

| Stripling v. Jordan Production Co.,<br>234 F.3d 863 (5th Cir. 2000)69                                     |

| <i>TiVo, Inc. v. EchoStar Communications Corp.</i> ,<br>516 F.3d 1290 (Fed. Cir. 2008)41, 42              |

| Uniloc USA, Inc. v. Microsoft Corp.,<br>632 F.3d 1292 (Fed. Cir. 2011)                                    |

| United States v. Valencia,<br>600 F.3d 389 (5th Cir. 2010)                                                |

| <i>VirnetX, Inc. v. Cisco Systems, Inc.</i> ,<br>767 F.3d 1308 (Fed. Cir. 2014)24, 56, 62, 64             |

| Water Technologies Corp. v. Calco, Ltd.,<br>850 F.2d 660 (Fed. Cir. 1988)63                               |

| Wenske v. Blue Bell Creameries, Inc.,<br>C.A. No. 2017-0699-JRS, 2018 WL 5994971 (Del. Ch. Nov. 13, 2018) |

| Western Union Co. v. MoneyGram Payment Systems, Inc.,<br>626 F.3d 1361 (Fed. Cir. 2010)                   |

| <i>Williams v. Slade</i> ,<br>431 F.2d 605 (5th Cir. 1970)                                                |

| Wisconsin Alumni Research Foundation v. Apple Inc.,<br>905 F.3d 1341 (Fed. Cir. 2018)                     |

## STATUTES AND RULES

| 28 U.S.C.      |   |

|----------------|---|

| §1295(a)(1)    | 2 |

| §1331          | 2 |

| §1338          |   |

| 0              |   |

| 35 U.S.C. §284 |   |

| Fed. R. Civ. P. |    |

|-----------------|----|

| Rule 12(b)(6)   | 69 |

| Rule 16(b)      |    |

#### **OTHER AUTHORITIES**

| Glazier, Daniel & David Shine, Acquisitions and IP Licenses:   |    |

|----------------------------------------------------------------|----|

| Looking Out for Poison Pill Affiliate, 249 N.Y.L.J. 2 (2013)   | 69 |

| VLSI Technology LLC v. Intel Corp., No. 1:18-cv-00966-CFC-CJB, |    |

| Dkt. 846, Dkt. 847 (D. Del.)                                   | 69 |

#### STATEMENT OF RELATED CASES

This Court previously decided two mandamus petitions in this case: *In re Intel Corporation*, No. 2021-105, 841 F. App'x 192 (Fed. Cir. 2020) (per curiam) (Prost, C.J., Lourie & Chen, JJ.) (granting Intel's mandamus petition and vacating the district court's first order retransferring this case from Austin to Waco for trial); and *In re Intel Corporation*, No. 2021-111, 843 F. App'x 272 (Fed. Cir. 2021) (per curiam) (Prost, C.J., Lourie & Chen, JJ.) (subsequently denying Intel's mandamus petition challenging the district court's second order retransferring this case from Austin to Waco for trial). This Court also previously dismissed the following appeals challenging the PTAB's discretionary decision not to institute *inter partes* review ("IPR") of several patents including the two at issue in this appeal: *Intel Corporation v. VLSI Technology LLC*, Nos. 21-1614, -1616, -1617, 2021 WL 5968443 (Fed. Cir. May 5, 2021) (Prost, C.J., joined by O'Malley & Wallach, JJ.).

The Court's decision in this appeal may directly affect or be directly affected by the following pending cases: *VLSI Technology LLC v. Intel Corporation*, No. 6:21-cv-00299-ADA (formerly No. 6:19-cv-255-ADA) (W.D. Tex.); *VLSI Technology LLC v. Intel Corporation*, No. 1:19-cv-00977-ADA (formerly No. 6:19cv-256-ADA) (W.D. Tex.); *VLSI Technology LLC v. Intel Corporation*, No. 1:18cv-966-CFC (D. Del.); *VLSI Technology LLC v. Intel Corporation*, No. 5:17-cv05671-BLF (N.D. Cal.); and *Intel Corporation v. Fortress Investment Group, et al.*, No. 2021-0021-MTZ (Del. Ch.).<sup>1</sup>

In addition, the Court's decision in this appeal may directly affect or be directly affected by the following instituted IPR proceedings pending before the Patent Office, which are reviewing the patentability of all claims asserted in this case: *OpenSky Industries, LLC v. VLSI Technology LLC*, IPR2021-01064 (PTAB); *Patent Quality Assurance, LLC v. VLSI Technology LLC*, IPR2021-01229 (PTAB); *Intel Corporation v. VLSI Technology LLC*, IPR2022-00366 (PTAB) (joined with IPR2021-01064); and *Intel Corporation v. VLSI Technology LLC*, IPR2022-00479 (PTAB) (joined with IPR2021-01229).

Intel is unaware of any other case pending in this Court or any other court that will directly affect or be directly affected by the Court's decision in this appeal.

#### JURISDICTIONAL STATEMENT

The district court had jurisdiction under 28 U.S.C. §§1331, 1338 and entered final judgment on April 21, 2022. Appx98-100. Intel timely appealed on May 19, 2022. Appx4528-4530. This Court has jurisdiction under 28 U.S.C. §1295(a)(1).

<sup>&</sup>lt;sup>1</sup> This case and the two others filed by VLSI in the Western District of Texas were all previously consolidated under the caption *VLSI Technology LLC v. Intel Corporation*, No. 1:19-cv-00977-ADA (W.D. Tex.).

#### **INTRODUCTION**

This appeal arises from one of several lawsuits filed by VLSI Technology, LLC ("VLSI"), an entity formed by a hedge fund for the sole purpose of buying patents to assert against Intel Corporation ("Intel"). In the U.S. portion of its campaign, VLSI has sought to transform a *\$35 million* investment—the amount it paid to purchase over 170 patents—into more than *\$22 billion* in patent litigation damages through unsupported infringement theories and outrageous damages claims. This appeal, which comes after the first trial in VLSI's series of lawsuits, demonstrates how extreme VLSI's scheme is: after a six-day trial in Waco, Texas, a jury found that Intel infringed two old patents that were never practiced by the companies that owned them and awarded *\$2.175 billion* in damages. That award rests upon multiple errors and cannot be sustained.

To begin with, no reasonable jury could find infringement. For one patent, the literal-infringement verdict is unsupported because Intel's accused memory component can and does operate at a *lower* voltage than what VLSI's expert alleged was the claimed "*minimum* operating voltage." For the other patent, the jury's finding of infringement by equivalents cannot stand because it is barred by prosecution history estoppel and because VLSI's expert provided only conclusory equivalents testimony asserting that, contrary to the claim language, the *same* component in Intel's products both sends and receives the claimed "request."

Meanwhile, the entire verdict was tainted by irrelevant and prejudicial damages evidence that never should have been before the jury. On the last trial day, and over Intel's objections, the district court allowed VLSI to introduce six prior agreements where Intel had paid amounts ranging from \$200 million to \$1.5 billion to settle unrelated litigation and to license hundreds of unrelated patents. There was no dispute that these agreements were *not comparable* to a hypothetical license to the asserted patents, as VLSI's own expert admitted. The district court nonetheless allowed VLSI to use the noncomparable agreements to portray Intel as a serial infringer who pays large amounts to license patents in litigation and to urge the jury to award similar amounts here—which is exactly what the jury did.

The district court likewise abandoned its gate-keeping role in allowing VLSI to present an unreliable—and exorbitant—damages model at trial. VLSI's damages expert did not rely on the asserted patents' purchase price or any comparable licenses to determine a reasonable royalty. He instead devised a convoluted, made-for-litigation damages methodology that contravened this Court's precedent in several ways. In particular, VLSI's expert violated apportionment principles by creating a regression model that included *products and features not accused of infringement* and by relying on technical inputs purporting to measure the patented features' benefits that were similarly derived using *non-accused products and features*. VLSI's expert also allocated *all* of Intel's incremental profits to VLSI, even though

such profit disgorgement was neither legally nor factually supported. And contrary to the entire market value rule, VLSI's expert prejudicially compared the revenues he deemed attributable to the asserted patents with Intel's *total accused revenues*.

Adding further error, the district court refused to allow Intel to add a license defense that arose during this litigation following an acquisition made by the hedge fund that formed and controls VLSI. Although Intel moved to amend its answer three months before the trial occurred, the court did not rule on Intel's motion for *16 months* and then denied it as untimely and futile. That decision not only unfairly punished Intel for the court's own delay, but also misapprehended the license's plain language.

For these reasons, the judgment should be reversed or at least vacated and remanded.

#### **STATEMENT OF ISSUES**

1. Whether the '373 patent infringement judgment should be reversed because no reasonable jury could find that Intel's products literally store or use a "minimum operating voltage" as the claims require.

2. Whether the '759 patent infringement judgment should be reversed because prosecution history estoppel bars VLSI's equivalents theory and no reasonable jury could find that Intel's products satisfy the "request" limitations.

- 5 -

3. Whether a new trial is required because the district court erroneously and prejudicially allowed VLSI to introduce noncomparable Intel settlement agreements.

4. Whether a new trial is also required because the district court erroneously allowed VLSI to: (a) present an unreliable damages theory, which depended on a regression model and technical inputs that included non-accused products and features; (b) seek disgorgement of Intel's profits; and (c) introduce Intel's total accused revenues.

5. Whether the district court abused its discretion by not allowing Intel to add a license defense that arose during the litigation.

#### **STATEMENT OF FACTS**

#### A. VLSI's Serial Lawsuits Against Intel

VLSI was formed in 2016 by Fortress Investment Group LLC ("Fortress"), a New York-based hedge fund represented by VLSI's counsel. Appx3860; Appx4061(9:17-23); Appx4952-4953. Fortress is owned by SoftBank Group Corporation, an international holding company with over \$400 billion in assets that runs the world's largest technology fund. Appx3863.

Three days after its formation, VLSI began acquiring patents from NXP Semiconductors ("NXP"). Appx3981-3983. Over the next few years, VLSI purchased more than 170 NXP patents—including the two patents-in-suit—for a total payment of \$35 million. Appx13952-14079; Appx1729-1739. VLSI has just two employees and has never made or sold any products. Appx1685-1687. Its only business has been asserting former NXP patents against Intel.

VLSI initially sued Intel in California and Delaware alleging infringement of thirteen patents. In March 2019, VLSI filed another suit in Delaware adding six patents. One month later, VLSI dismissed the second-filed Delaware suit and refiled it as three actions (with two additional patents) in Texas. This appeal arises from the first Texas case and involves U.S. Patent Nos. 7,523,373 ("373 patent") and 7,725,759 ("759 patent").<sup>2</sup>

#### B. VLSI's Assertion Of The '373 Patent

#### 1. The '373 patent

The '373 patent relates to "a minimum memory operating voltage technique." Appx105(1:6-9). A memory, which stores data, must be provided with a power supply voltage to operate. Appx1383; Appx1914-1916. A "minimum operating voltage" is the *lowest* voltage at which the memory can reliably operate (e.g., write, read, or retain data). Appx1403; Appx1917-1920; Appx2730-2731.

The patent describes a technique that involves first determining a memory's "minimum operating voltage" and storing that value. Appx101(abstract). "This

<sup>&</sup>lt;sup>2</sup> NXP came to own these patents after acquiring Freescale, which had acquired Sigmatel. Appx1299. Sigmatel, Freescale, and NXP never used the claimed inventions in any products. Appx1296-1297; Appx1301-1302; Appx1367-1368.

minimum operating voltage information can then be used in determining when an alternative power supply voltage may be switched to the memory[.]" *Id*.

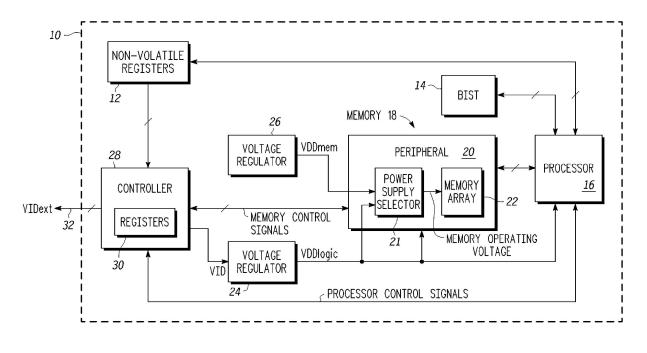

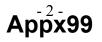

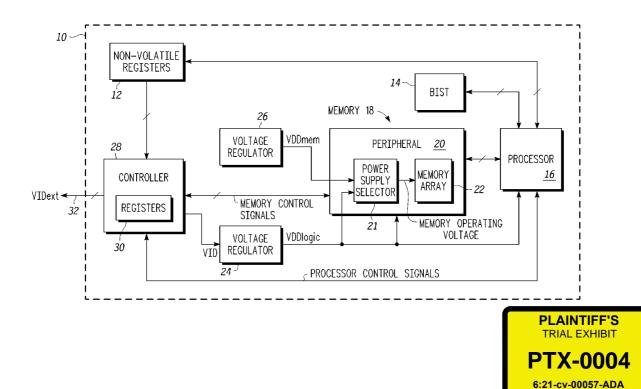

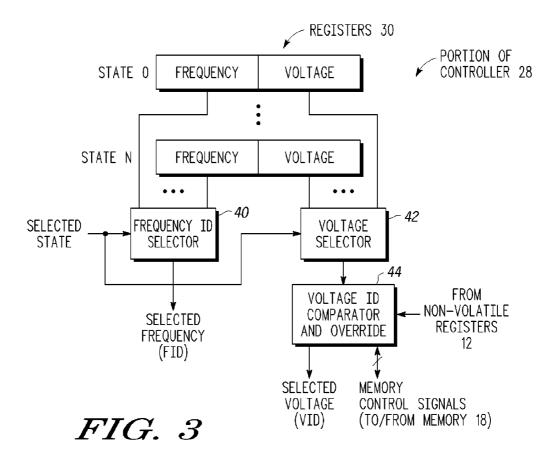

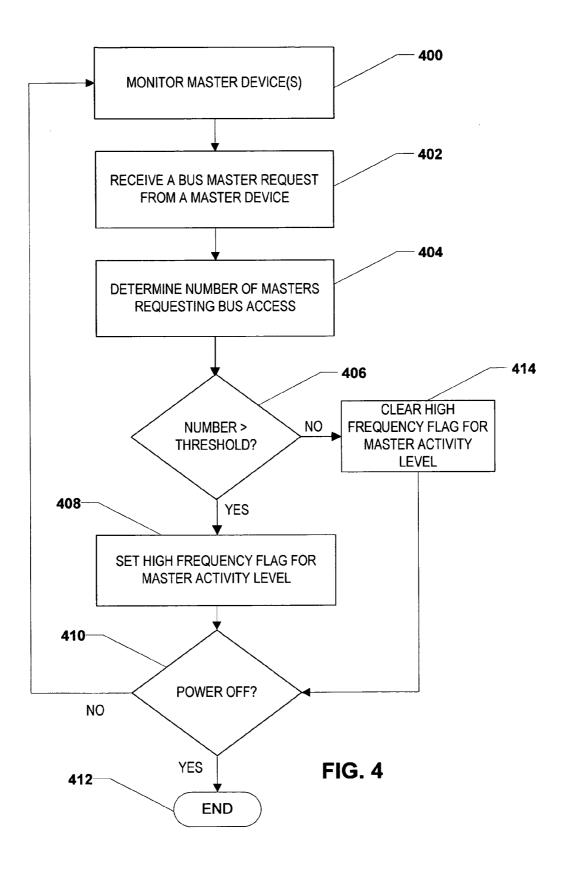

Figure 1 is shown below:

## *FIG.* 1

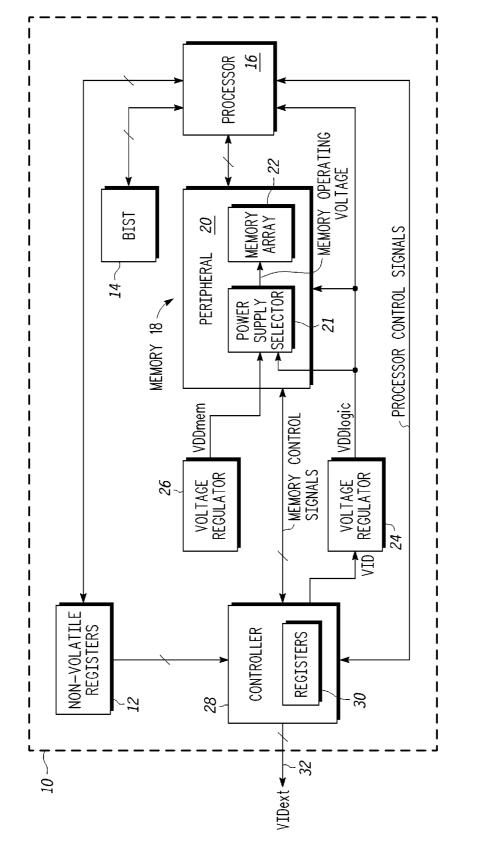

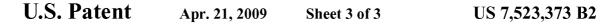

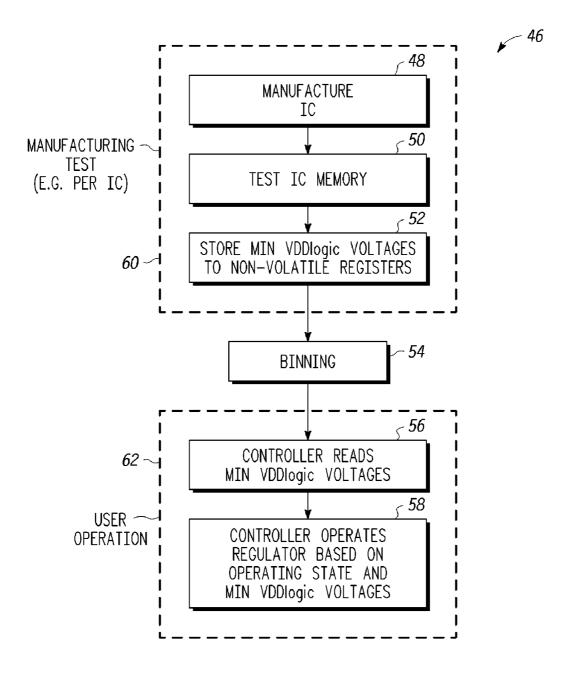

Appx102. In this embodiment, a minimum operating voltage of memory 18 is stored in registers 12. Appx107(6:30-36). Controller 28 and power supply selector 21 use that stored minimum operating voltage to determine which of two regulated voltages (VDDmem or the lower VDDlogic) to supply to the memory as its operating voltage. Appx105-107(2:52-3:29, 5:42-53). When VDDlogic is at least the value of the memory's minimum operating voltage, VDDlogic is provided to the memory. Otherwise, VDDmem is supplied to the memory. Appx106(3:30-44, 3:54-4:7).

VLSI asserted claims 1, 5, 6, 9, and 11. Representative claim 1 provides:

1. A method, comprising:

providing an integrated circuit with a memory;

operating the memory with an operating voltage;

#### determining a value of a minimum operating voltage of the memory;

providing a non-volatile memory (NVM) location;

*storing the value of the minimum operating voltage of the memory* in the NVM location;

providing a functional circuit on the integrated circuit exclusive of the memory;

providing a first regulated voltage to the functional circuit;

- providing a second regulated voltage, the second regulated voltage is greater than the first regulated voltage;

- providing the first regulated voltage as the operating voltage of the memory *when the first regulated voltage is at least the value of the minimum operating voltage*; and

- providing the second regulated voltage as the operating voltage of the memory *when the first regulated voltage is less than the value of the minimum operating voltage*, wherein while the second regulated voltage is provided as the operating voltage of the memory, the first regulated voltage is provided to the functional circuit.

Appx111(13:7-28).<sup>3</sup>

Independent claim 9 is similar. It recites "a memory location that stores a value representative of the minimum operating voltage" of the memory, and a

<sup>&</sup>lt;sup>3</sup> Emphasis is added unless indicated otherwise.

"power supply selector" that supplies either a "first regulated voltage" or a "second regulated voltage" to the memory based on the same relationship between the first regulated voltage and the memory's minimum operating voltage as in claim 1. Appx111(13:59-14:15).

#### 2. Intel's accused C6SRAM multiplexer

VLSI accused Intel's Haswell and Broadwell microprocessors of infringing the '373 patent. Appx1447. Each microprocessor chip includes multiple processor cores, which operate in different "states" depending on performance needs, plus various memories and other components. Appx1841-1845.

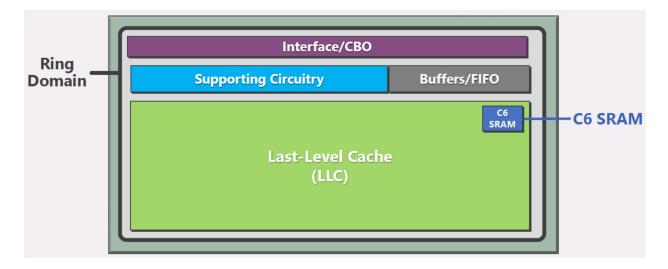

VLSI's infringement claim focused on Intel's C6SRAM. Appx1453. The C6SRAM is a small memory that, along with the last-level cache memory and other components, collectively form the "ring" domain:

Appx15344; *see* Appx1842-1845; Appx2726-2727. The C6SRAM serves one purpose: it stores processor state data when an associated processor core is turned off (or "sleeping"). Appx1395; Appx1833-1834; Appx1938.

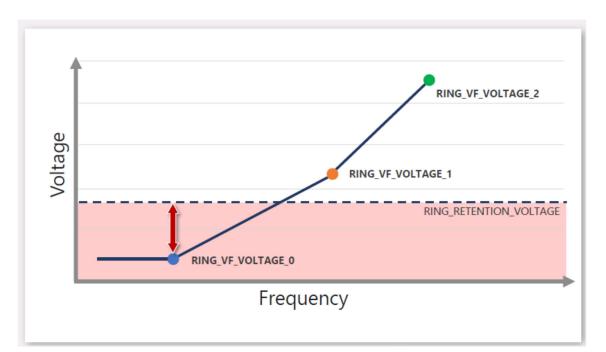

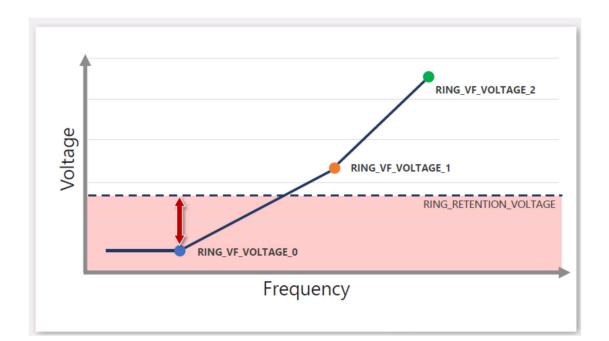

Under most circumstances, the ring components (including the C6SRAM) receive a voltage from the "VCCR" supply. Appx1845; Appx1939. During operational states when the chip's processor cores are awake, the VCCR voltage level is set based on a value stored in one of the RING\_VF\_VOLTAGE\_0, RING\_VF\_VOLTAGE\_1, or RING\_VF\_VOLTAGE\_2 fuses<sup>4</sup>:

Appx15343; *see* Appx1850-1855; Appx1949-1950; Appx2757-2760. During certain states when some processor cores are asleep, the VCCR voltage level is set

<sup>&</sup>lt;sup>4</sup> A "fuse" stores information and does not lose its value when removed from power. Appx1853. Intel sets the fuse values in each chip during manufacturing. Appx2678.

based on the RING\_RETENTION\_VOLTAGE fuse value. Appx1859-1861; Appx1951. As illustrated above, RING\_RETENTION\_VOLTAGE is *not* the C6SRAM's lowest operating voltage as it is *greater than* RING\_VF\_VOLTAGE\_0. Appx1860; Appx1945-1950; Appx2015-2017; Appx2742-2744; Appx15342.

Whenever the chip enters a deep sleep state called "Package C7" (i.e., when *all* processor cores are asleep (Appx1388)), a multiplexer switches the C6SRAM's voltage supply from VCCR to a second supply called "VCCIO" and the ring components other than the C6SRAM are essentially turned off. Appx1845-1849; Appx1862-1865; Appx1939-1940; Appx1960; Appx2669-2670. RING\_RETENTION\_VOLTAGE is *not* involved in this voltage-switching process. Appx1862; Appx2744-2747.

#### C. VLSI's Assertion Of The '759 Patent

#### 1. The '759 patent

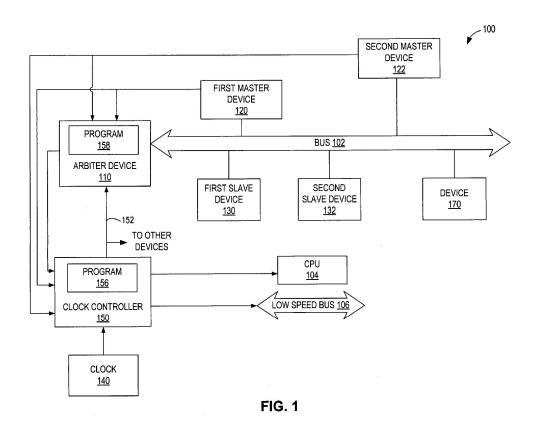

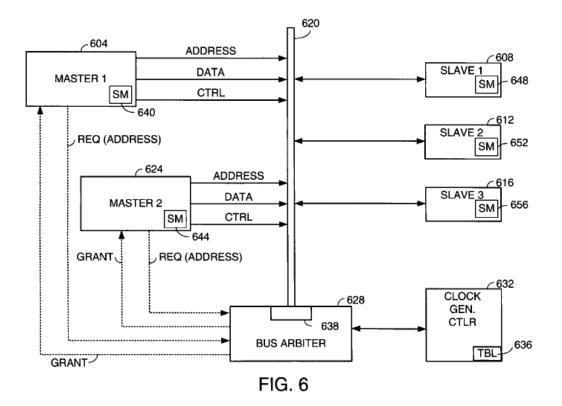

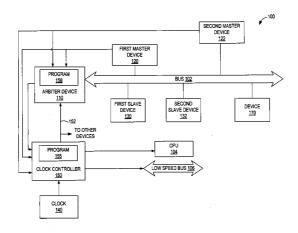

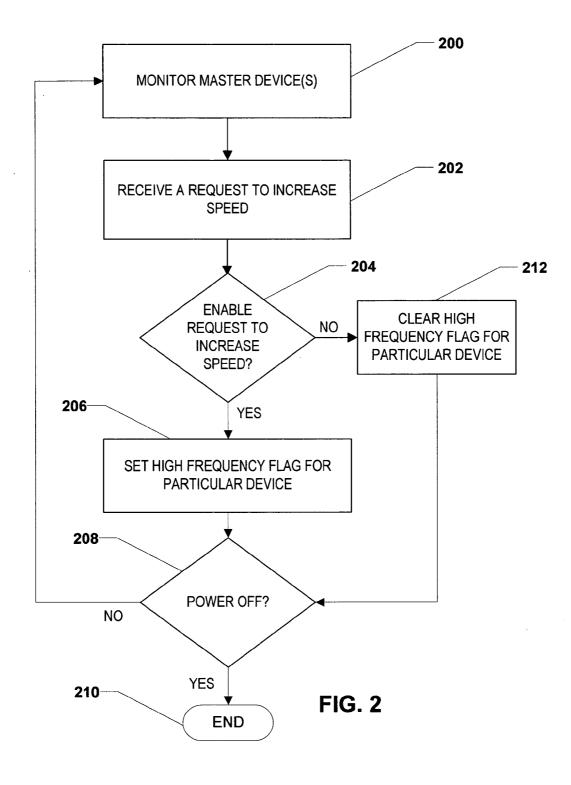

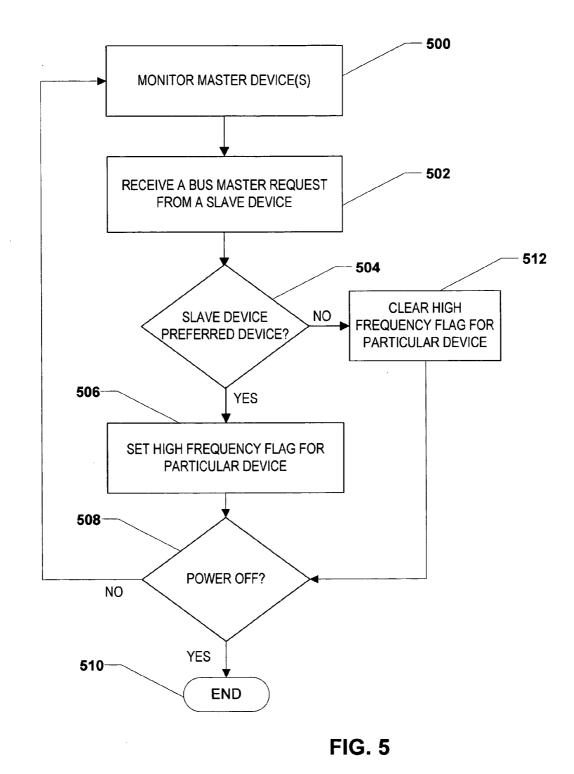

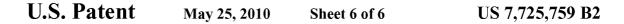

The '759 patent relates to "managing clock speeds within electronic devices." Appx120(1:6-7). Clock speed, or frequency, is the speed at which the electronic device operates. Appx1384. The '759 patent describes a technique for managing clock speed where a "first master device" (120 below) sends a "request" to a "clock controller" (150) to change the frequency of a "bus" (102) and other devices (e.g., 122) connected via the bus:

Appx114.

VLSI asserted claims 14, 17, 18, and 24. Representative claim 14 provides:

14. A system comprising:

a bus capable of operation at a variable clock frequency;

a first master device coupled to the bus, *the first master device configured to provide a request to change a clock frequency of a high-speed clock* in response to a pre-defined change in performance of the first master device, wherein the predefined change in performance is due to loading of the first master device as measured within a predefined time interval; and

*a programmable clock controller* having an embedded computer program therein, the computer program including instructions to:

receive the request provided by the first master device;

provide the clock frequency of the high-speed clock as an output to control a clock frequency of a second master device coupled to the bus in response to receiving the request provided by the first master device; and

provide the clock frequency of the high-speed clock as an output to control the variable clock frequency of the bus in response to receiving the request provided by the first master device.

Appx123-124(8:50-9:4). Independent claim 18 similarly recites a system where "the *clock controller* [is] configured to *receive a request* to change the clock frequency of the high-speed clock *from the first master device*[.]" Appx124(9:19-40).

During prosecution, the applicant amended the claims eight times, including to overcome rejections based on U.S. Patent No. 7,007,121 ("Ansari"). Among those amendments, the applicant canceled claims reciting that "*at least* one master device" provide an input "includ[ing] a request to change the variable clock frequency" (Appx8316-8317), and rewrote the claims to more narrowly require that "the master device ... provide a request to change the clock frequency" (Appx8368).

#### 2. Intel's accused SpeedShift feature

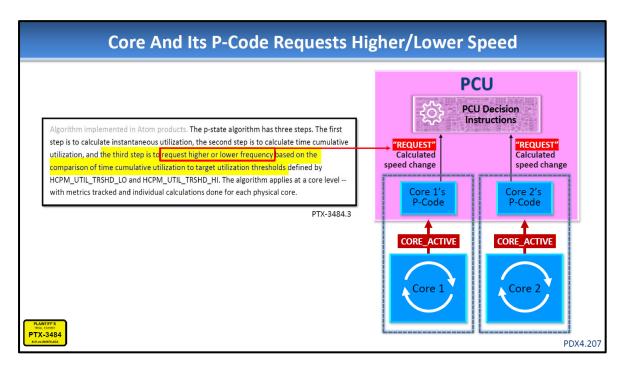

VLSI accused Intel's "Lake" microprocessors of infringing the '759 patent. Appx1462. VLSI's infringement claim focused on Intel's SpeedShift technology a collection of sophisticated algorithms that Intel's engineers developed to autonomously manage power and performance. Appx2073-2074; Appx2179-2183. These algorithms are implemented in source code (called "p-code") running on the power control unit ("PCU"), which is a separate component from the processor cores whose power and performance they manage. Appx2137; Appx2697; Appx2748-2751. Intel's processor cores do not send requests to change frequency based on changes in their own individual performance. Instead, the PCU decides whether to change frequency based on SpeedShift's ongoing observations of the system as a whole. Appx2083-2085; Appx2188-2189.

#### **D.** Intel's License Defense

In July 2020, Fortress—which formed and controls VLSI—acquired control of Finjan Holdings, LLC ("FHL"). Appx3009. That acquisition triggered Intel's rights under a 2012 license to practice patents owned by FHL's subsidiaries and their "Affiliates," a broadly-defined term that includes VLSI. Appx3684(§1.2). In August 2020, Intel notified VLSI and Fortress that the acquisition meant Intel had a license to VLSI's asserted patents. Appx3017-3019. Intel moved to stay the litigation in September 2020 and to amend its answer to add this license defense in November 2020. Appx3001-3015; Appx3631-3644.

#### E. Trial

In December 2020, over Intel's objections, the district court transferred the case from Austin to Waco for trial. Appx3841-3851. Trial was held during February/March 2021.

#### 1. Fortress evidence

The district court initially ruled there was "no way to not allow a discussion of VLSI's relationship with Fortress" at trial because it was relevant to the jury's understanding of VLSI, assessing damages, and determining witness credibility. Appx4874. After all, Fortress created VLSI, arranged for VLSI's purchase of the patents-in-suit, holds a majority of VLSI's board seats, and would share in any recovery. Appx3975-3976; Appx3856-3857. Before opening statements, however, the court reversed course and precluded Intel from mentioning Fortress during trial. Appx3947-3951.

#### 2. VLSI's infringement case

VLSI presented its infringement case through its expert Tom Conte. For the '373 patent, Dr. Conte testified that RING RETENTION VOLTAGE was *literally* the claimed "minimum operating voltage" of Intel's C6SRAM. Appx1451; Appx2727-2728. He offered that opinion even though the C6SRAM can and does operate at a lower voltage. Infra pp. 27-30. Dr. Conte also contended that a multiplexer selects which voltage to provide to the C6SRAM in the claimed manner, despite admitting the that multiplexer does actually not use RING RETENTION VOLTAGE (the alleged "minimum operating voltage") when making that selection. Appx2735-2736.

For the '759 patent, Dr. Conte presented a doctrine-of-equivalents theory as an alternative to literal infringement, but that theory encompassed claim scope surrendered during prosecution. Appx2704. More specifically, Dr. Conte testified that the *combination* of a processor core (the alleged "first master device") and p-code running on the PCU (the alleged "clock controller") provided the claimed "request" to change frequency. Appx2705-2709; Appx15183-15186. Dr. Conte did not explain how this combination operated in substantially the same way as the claimed invention. Nor could he show how his equivalents theory—where the PCU (the alleged "clock controller") sends the claimed request to itself—comports with the claim language, which requires the master device to "provide" and the clock controller to "receive" the request. *Infra* pp. 42-45.

#### 3. Damages evidence

After denying Intel's *Daubert* challenges, the district court allowed VLSI to present its damages case through its expert Ryan Sullivan. Appx1-2. Dr. Sullivan relied on a regression model—which he created only for litigation and which included *non-accused products and features* (*e.g.*, Appx1713; Appx1720-1721)— to purportedly determine the relationship between frequency and price in Intel's products. Appx1611-1614. He multiplied that result by the purported power and performance benefits attributable to the patents, as determined through testing done by VLSI expert Murali Annavaram—which again included *non-accused products*

*and features* (*e.g.*, Appx1555-1566). Appx1606-1607; Appx1654-1658; Appx1702-1704; Appx15290; Appx15293.<sup>5</sup> Dr. Sullivan applied that number to Intel's accused revenues to calculate the revenues allegedly attributable to the accused features. Appx1654-1658. He then performed a so-called "cost and contribution apportionment" step in which he subtracted Intel's spending costs from the calculated revenues and allocated the entire result—i.e., *all* of Intel's alleged incremental profits—to VLSI. Appx1658-1664; Appx15294. From those calculations, Dr. Sullivan concluded that a reasonable royalty would be \$1.61 billion for the '373 patent and \$832 million for the '759 patent. Appx1663-1664; Appx15303; Appx15305.

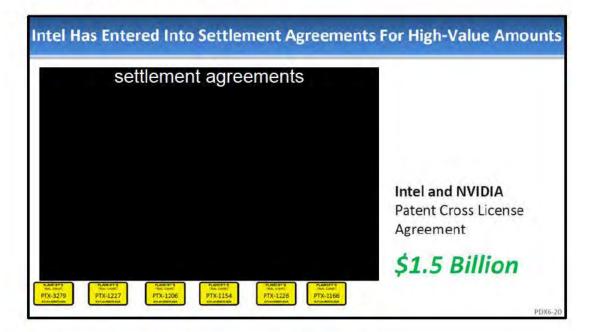

On the last trial day, the district court overruled Intel's objections<sup>6</sup> and allowed VLSI to introduce evidence of six *noncomparable* agreements in which Intel had paid between \$200 million and \$1.5 billion to settle unrelated litigation and to license hundreds of unrelated patents. Appx2328-2331; Appx2804-2808.

Intel subsequently called its damages expert Hance Huston. He testified that a reasonable royalty would be \$2.2 million, based on prior transactions involving the asserted patents and 20 agreements that he explained were *comparable* to the

<sup>&</sup>lt;sup>5</sup> Dr. Sullivan assumed a 1% frequency increase equaled a 1% performance or power savings increase. Appx1606-1607.

<sup>&</sup>lt;sup>6</sup> Appx3570-3579; Appx3626-3629; Appx3712-3713; Appx3722-3725; Appx3903-3904; Appx3986-3987; Appx2502; Appx2799-2801; Appx2804.

#### Case: 22-1906 Document: 17 Page: 35 Filed: 09/14/2022 CONFIDENTIAL MATERIAL FILED UNDER SEAL REDACTED

hypothetical license. Appx2374; Appx2764-2784; *see* Appx2370-2381; Appx15392-15409. On cross-examination, and over Intel's continuing objection, VLSI brought up the *noncomparable* Intel settlements—emphasizing that "Intel has paid much more than single-digit millions to license[] patents in litigation," including "\$1.5 billion to license patents from ... NVIDIA[.]" Appx2800-2802.

VLSI then called its licensing expert Mark Chandler for the first time in its rebuttal case—and as the last trial witness. Mr. Chandler agreed that the six Intel settlement and cross-license agreements were *"not comparable"* to a hypothetical license to the asserted patents. Appx2513; Appx2516-2517; *see* Appx2807-2808. He nevertheless testified that these agreements would have been "informative" to the hypothetical negotiation (Appx2515-2516) and emphasized the "high-value" amounts Intel paid for each settlement:

Appx15236; see Appx2803-2806; Appx15231-15236.

# Case: 22-1906 Document: 17 Page: 36 Filed: 09/14/2022 CONFIDENTIAL MATERIAL FILED UNDER SEAL REDACTED

#### 4. Verdict

The next day, the jury found that Intel infringed the '373 patent literally and the '759 patent by equivalents (but not literally). Appx9-10. The jury also found that Intel had not proved the '759 patent invalid. Appx12.

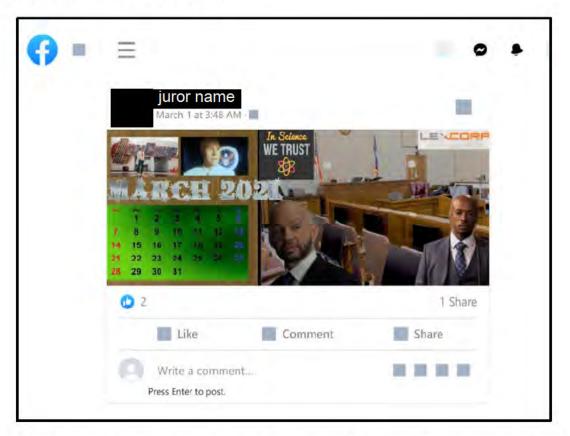

The jury awarded \$1.5 billion for the '373 patent and \$675 million for the '759 patent. Appx13-14. Although these amounts did not match the reasonable-royalty numbers presented by any expert, they did match what Intel paid to settle two of the unrelated litigations that VLSI told the jury about. In fact, the jury's \$1.5 billion award matched a number found only one place in the record: Intel's settlement payment to NVIDIA. Appx2805. And the jury's \$675 million award matched Intel's settlement payment to Intergraph as reported by the *New York Times*. Appx4047-4048. That the jury awarded this precise amount, which was not stated at trial, was either a remarkable coincidence or an indication the jury consulted extra-record material—as VLSI's counsel suggested during closing arguments and later events involving one juror confirmed had occurred. *See infra* p. 21.<sup>7</sup>

<sup>&</sup>lt;sup>7</sup> Mr. Chandler testified that the Intergraph settlement was for <sup>settlement amount</sup> (Appx2805), but VLSI's counsel stated during closing that what Intel paid in one settlement "was published in the New York Times" (Appx2622). A simple Internet search returns the *New York Times* article and others reporting the Intergraph amount as \$675 million. Appx4046-4058.

Case: 22-1906 Document: 17 Page: 37 Filed: 09/14/2022 CONFIDENTIAL MATERIAL FILED UNDER SEAL REDACTED

### F. Post-Trial Proceedings

### 1. Intel's juror misconduct motion

After the verdict, Intel learned that—despite admonitions not to research or communicate about the case (Appx1182-1185; Appx2305)—a juror posted the following on Facebook *during trial*:

Appx4040. The juror's post depicted actors who played Superman villain Lex Luthor, likening Intel to Luthor's international conglomerate "LexCorp." This was superimposed on a photograph of the Waco courtroom where trial was held—taken from the "IPWatchdog" blog. Appx4039-4045.

Intel moved for a new trial because the Facebook post showed the juror improperly communicated about the case during trial and consulted extra-record information. Appx4015-4038. In September 2021, the district court denied Intel's motion and refused to hold an evidentiary hearing to investigate the juror's misconduct and its impact on the verdict. Appx4508-4520.

### 2. Intel's other post-trial motions

In August 2021 and March 2022, the district court rejected Intel's requests for JMOL or a new trial on infringement, invalidity, and damages. Appx16-22; Appx74-97. The court separately ruled that prosecution history estoppel did not bar VLSI's equivalents theory for the '759 patent. Appx49-53.

#### 3. Intel's license defense

In March 2022, the district court also denied Intel's motion to add its license defense—which Intel had filed 16 months earlier—on the grounds that Intel's motion was untimely, amendment was futile, and VLSI would be prejudiced because trial already occurred. Appx65-73.

#### 4. Final judgment

In April 2022, the district court awarded \$162 million in pre-judgment interest and entered judgment. Appx98-100; Appx4521-4527.

#### **SUMMARY OF ARGUMENT**

1. The infringement judgment for the '373 patent should be reversed. No reasonable jury could find that RING\_RETENTION\_VOLTAGE is *literally* a "*minimum* operating voltage" of Intel's C6SRAM because the evidence established that the C6SRAM can and does operate at a *lower* voltage. Nor could a reasonable jury find that Intel's products use RING\_RETENTION\_VOLTAGE (the alleged "minimum operating voltage") in determining "when" to provide either of two voltages to the C6SRAM as the claims require. Instead, Intel's products switch the C6SRAM's voltage supply whenever the chip enters the Package C7 sleep state—without consideration of RING\_RETENTION\_VOLTAGE.

2. The infringement judgment for the '759 patent should likewise be reversed. Prosecution history estoppel bars the jury's equivalents finding because, to overcome prior-art rejections, the applicant narrowed the claims by amending them to require that "the master device" (rather than "the *at least* one master device") provide the request to change frequency, and VLSI's equivalents theory improperly sought to recapture the surrendered claim scope. Additionally, substantial evidence does not support the jury's infringement finding because Dr. Conte offered only conclusory testimony on equivalents, and his nonsensical theory—where the PCU (the alleged "clock controller") *both* sends and receives the request to change frequency—is incompatible with the claim language, which requires the master

device to "provide" the request and the clock controller to "receive the request provided by the first master device."

3. A new trial is required because the district court erroneously and prejudicially allowed VLSI to introduce six agreements where Intel had paid between \$200 million and \$1.5 billion to settle unrelated litigation and to license hundreds of unrelated patents. VLSI's own licensing expert admitted that these agreements were *not comparable* to a hypothetical license to the asserted patents. And contrary to the district court's post-trial rationalization, VLSI's last-minute introduction of these noncomparable agreements was not "proper rebuttal" to Intel's damages expert, who presented a traditional reasonable-royalty analysis based on prior transactions involving the asserted patents and several *comparable* agreements. VLSI unfairly used the noncomparable agreements to portray Intel as a serial infringer who pays large amounts to license patents in litigation, which inflated the jury's damages analysis and tainted the entire verdict.

4. A new trial is also warranted because VLSI's damages theory should have been excluded and cannot support the jury's award. VLSI was required "to seek only those damages attributable to the infringing features." *VirnetX, Inc. v. Cisco Sys., Inc.*, 767 F.3d 1308, 1326 (Fed. Cir. 2014). Yet VLSI's damages expert applied a regression analysis that included *non-accused products and features*, while failing to include the accused features, and relied on technical inputs regarding

- 24 -

the patented features' purported benefits that were similarly derived using *non-accused products and features*. He then allocated *all* of Intel's incremental profits to VLSI, though such disgorgement of profits was neither a viable legal remedy nor factually supported. Finally, VLSI's expert prejudicially compared the revenues he attributed to the asserted patents with Intel's *total accused revenues* in violation of the entire market value rule.

5. The district court abused its discretion by not allowing Intel to add a license defense that arose during the litigation. As a result of a prior license agreement, Intel became licensed to the '373 and '759 patents when Fortress—which formed and controls VLSI—acquired a Finjan entity in July 2020. Intel's amendment was timely, as Intel promptly notified VLSI and the court about its license defense and moved to amend its answer while following the dispute resolution procedures required by the license itself. Intel's amendment was not futile because the license's plain language—under which VLSI is an "Affiliate" due to Fortress's control of VLSI—makes clear that the license applies here.

#### ARGUMENT

#### I. STANDARD OF REVIEW

The Fifth Circuit reviews the denial of JMOL *de novo*. *ACCO Brands, Inc. v. ABA Locks Mfrs. Co.*, 501 F.3d 1307, 1311-1312 (Fed. Cir. 2007). Evidentiary rulings and rulings on motions to amend pleadings are reviewed for abuse of discretion. *Knight v. Kirby Inland Marine Inc.*, 482 F.3d 347, 351 (5th Cir. 2007); *Meaux Surface Protection, Inc. v. Fogleman*, 607 F.3d 161, 167 (5th Cir. 2010). An "erroneous view of the law" is "necessarily" an abuse of discretion. *Highmark Inc. v. Allcare Health Mgmt. Sys., Inc.*, 572 U.S. 559, 563 n.2 (2014).

Infringement and damages are reviewed for substantial evidence following a jury verdict. *Lucent Techs., Inc. v. Gateway, Inc.*, 580 F.3d 1301, 1309-1310 (Fed. Cir. 2009). Whether prosecution history estoppel applies is reviewed *de novo*. *Pharma Tech Solutions, Inc. v. LifeScan, Inc.*, 942 F.3d 1372, 1380 (Fed. Cir. 2019). Factual findings made by the court are reviewed for clear error. *Festo Corp. v. Shoketsu Kinzoku Kogyo Kabushiki Co.*, 493 F.3d 1368, 1376 (Fed. Cir. 2007).

# II. THE INFRINGEMENT JUDGMENT FOR THE '373 PATENT SHOULD BE REVERSED.

The jury found *literal* infringement of the '373 patent. Appx9.8 However,

there was no substantial evidence that Intel's products store or use a "minimum operating voltage" of the C6SRAM as the claims require.

# A. Intel's Products Do Not Store The Claimed "Minimum Operating Voltage."

Each asserted claim requires storing "the value of the minimum operating voltage of the memory" or "a value representative of the [memory's] minimum

<sup>&</sup>lt;sup>8</sup> VLSI abandoned its doctrine-of-equivalents assertion for this patent at trial. Appx1451; *see* Appx3807-3808.

operating voltage." Appx111(13:13-14, 13:63-64). VLSI identified Intel's C6SRAM as the accused "memory" and the RING\_RETENTION\_VOLTAGE fuse value as the accused "minimum operating voltage." Appx1403-1404; Appx2661-2662; Appx15091; Appx15097.

VLSI's expert Dr. Conte testified that RING\_RETENTION\_VOLTAGE is the "minimum retention voltage" of the C6SRAM, and he identified no other supposed "minimum operating voltage." Appx2727-2728; *see* Appx2656-2657; Appx2661; Appx2725; Appx2730-2731. Dr. Conte agreed that a "minimum retention voltage" is "the *minimum* voltage required to hold data." Appx2730; Appx2730-2731 ("minimum" means "the *lowest* value"). "In other words," Dr. Conte explained, "you['ve] got to keep power on the memory and you['ve] got to keep *above* this" minimum value. Appx1403.

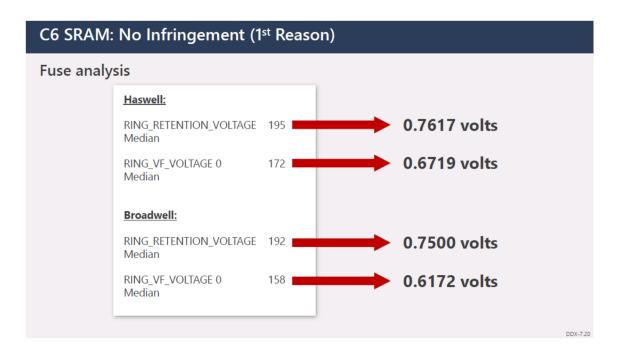

But Intel's RING\_RETENTION\_VOLTAGE is merely *a* voltage at which the C6SRAM *can* retain data, not the *"minimum"* voltage at which data retention occurs. As Intel's engineers explained, the C6SRAM is "fully operational" and retains data at a RING\_VF\_VOLTAGE\_0 voltage that is *lower* than RING\_RETENTION\_VOLTAGE:

Appx15343; Appx15322; Appx1854-1855; *see* Appx1859-1861 ("Q. From a voltage perspective, is RING\_RETENTION\_VOLTAGE level higher or lower than Ring\_VF\_Voltage\_0? A. The voltage level is higher."); Appx2757-2760; Appx14252-14280.

Intel's expert Dennis Sylvester confirmed this fact by analyzing fuse data taken from the actual accused products. He explained that the RING\_VF\_VOLTAGE\_0 values (which have a median value of 0.6719 volts in Haswell and 0.6172 volts in Broadwell across millions of individual chips) are *"significantly lower"* than the RING\_RETENTION\_VOLTAGE values (which have a median value of 0.7617 volts in Haswell and 0.7500 volts in Broadwell):

Appx15342; Appx1945-1950; *see* Appx2015 ("Ring\_VF\_Voltage\_0 was significantly below [0.75 volts] in the data I actually collected from the products."); Appx2015-2017; Appx2742-2744; Appx14224-14251.

VLSI's expert Dr. Conte agreed that RING\_RETENTION\_VOLTAGE is set to about 0.75 or 0.76 volts in Intel's products. Appx2731. Yet he admitted on crossexamination that, when he conducted his infringement analysis, he did not investigate whether the C6SRAM ever operates at voltages *below* that RING\_RETENTION\_VOLTAGE. Appx2732. And when confronted with Intel's evidence about RING\_VF\_VOLTAGE\_0, Dr. Conte agreed "[i]t's a *voltage* that's actually used" in Intel's products. Appx2436-2437. Given this evidence, no reasonable jury could find that RING\_RETENTION\_VOLTAGE\_\_\_\_which is *greater*  than RING\_VF\_VOLTAGE\_0—is *literally* the "*minimum* retention voltage" (or any other "*minimum* operating voltage") of the C6SRAM.

The district court nonetheless denied JMOL, relying primarily on Dr. Conte's testimony claiming that Intel's witnesses failed to account for "inverse temperature dependence" (voltage adjustments based on temperature) and his unsupported conclusion that, when those adjustments are made, the operating *voltage* derived RING VF VOLTAGE 0 fuse value is always greater than from the RING RETENTION VOLTAGE. Appx78 (citing Appx2425-2432; Appx2434-2437; Appx2450-2452). But Dr. Conte never explained what those supposed RING VF VOLTAGE 0 voltages were and never performed any calculations to show how Intel's RING VF VOLTAGE 0 voltages supposedly should have been adjusted. The only voltages for RING VF VOLTAGE 0 presented to the jury were from Intel's expert's analysis of the fuse data taken from the accused products, and it is *undisputed* that those voltages were "significantly lower" than RING RETENTION VOLTAGE. Supra pp. 27-30.

Ignoring that Dr. Conte never identified any RING\_VF\_VOLTAGE\_0 voltages used in Intel's products, the district court found that Dr. Conte's ultimate conclusion was "corroborated" by a few pages from Intel's documents. Appx78. It was not. None of the documents cited by the court (or otherwise relied on by VLSI) specified the voltages for RING\_VF\_VOLTAGE\_0 in Intel's products, much less

showed that they are always greater than RING\_RETENTION\_VOLTAGE as Dr. Conte contended.

For example, the district court referenced a draft Intel specification showing a "Vretention" line below a "v/f 0" point on a graph and Dr. Conte's unsupported say-so that this "Vretention" was RING\_RETENTION\_VOLTAGE. Appx14103; Appx2425-2426. This document, however, describes a generic voltage at which data retention occurs ("Vretention"). Appx14103; Appx2017 ("That's just a line saying that you should be able to retain down below there."). It says nothing about the RING\_RETENTION\_VOLTAGE at the center of VLSI's infringement theory. Appx14103; Appx2016-2018. And this draft specification, which Dr. Conte agreed was "not a final description of the products" (Appx2435-2436), nowhere identifies the actual fuse settings or voltages implemented in Intel's products.

VLSI also relied on an Intel spreadsheet using the term "Vmin." Appx11359-11362. But Intel's expert—the only witness who discussed this document at trial explained that this "Vmin" refers to an "active voltage[] to meet performance specifications," not to any minimum operating voltage or minimum retention voltage, and has nothing to do with RING\_RETENTION\_VOLTAGE. Appx2013-2015.

The district court further pointed to two Intel specifications stating that "RING\_RETENTION\_VOLTAGE ... defines the worst case retention voltage *for*

**RING**." Appx9574; Appx12642; see Appx2656-2657. But, again, these documents do not identify any fuse values or voltages used in Intel's products. And as Dr. Conte admitted, these specifications indicate that RING RETENTION VOLTAGE applies not just to the C6SRAM, but to the entire ring domain which also includes the last-level cache memory. Appx2725-2728. The district court dismissed this distinction, stating that the patent does not "require that the RING RETENTION VOLTAGE apply to the C6 SRAM specifically." Appx79. But the claims require storing "the minimum operating voltage of the memory" (Appx111(13:13-14); see id.(13:63-64)), and VLSI identified only the C6SRAM as the accused "memory" (Appx1403). VLSI was therefore required to prove that RING RETENTION VOLTAGE is a "minimum operating voltage" of the C6SRAM, not of some larger collection of components containing the C6SRAM.<sup>9</sup>

Ultimately, Dr. Conte's hand-waving analysis cannot change the fact that the *only voltages* for RING\_VF\_VOLTAGE\_0 in Intel's products presented to the jury were undisputedly *lower* than RING\_RETENTION\_VOLTAGE. The evidence thus supports only one conclusion: RING\_RETENTION\_VOLTAGE is not *literally* a "*minimum* operating voltage" of the C6SRAM. Dr. Conte's unsupported opinion

<sup>&</sup>lt;sup>9</sup> The district court further stated that Dr. Conte's testimony was "corroborated" by source code. Appx77-78. But Dr. Conte simply said he reviewed Intel's code; he did not identify any code supporting his conclusions for this limitation. Appx2451-2452; Appx1380-1382; Appx1404.

to the contrary cannot sustain the infringement verdict. *Wisconsin Alumni Research Found. v. Apple Inc.*, 905 F.3d 1341, 1350 (Fed. Cir. 2018) (despite Dr. Conte's contrary expert conclusion, finding "insufficient evidence to support the jury's finding that [the accused] products literally satisfy the [disputed] limitation"); *Guile v. United States*, 422 F.3d 221, 227 (5th Cir. 2005) ("'A claim cannot stand or fall on the mere *ipse dixit* of a credentialed witness."").

## **B.** Intel's Products Do Not Provide The First And Second Regulated Voltages "When" The Claims Require.

Each asserted claim additionally requires using the memory's "minimum operating voltage" in determining which of two voltages to supply to the memory. Specifically, the claims require providing "as the operating voltage of the memory" (1) "the first regulated voltage ... *when the first regulated voltage is at least ... the minimum operating voltage*," and (2) "the second regulated voltage ... *when the first regulated voltage ... when the first regulated voltage ... when the first regulated voltage is less than [or below] ... the minimum operating voltage.*" Appx111(13:20-27, 14:8-13). As Dr. Conte acknowledged, these limitations "tell[] you when to use a different voltage" and both "refer to the minimum operating voltage." Appx2733-2734.

Even under VLSI's (incorrect) theory that RING\_RETENTION\_VOLTAGE is a "minimum operating voltage" of the C6SRAM, VLSI introduced no evidence that Intel's products ever use RING\_RETENTION\_VOLTAGE in determining "when" to provide each of the two regulated voltages as the claims require. In presenting his infringement opinion for these limitations, Dr. Conte testified that a multiplexer selects between two voltages to supply to the C6SRAM: (1) VCCR, which he called the "first regulated voltage"; and (2) VCCIO, which he called the "second regulated voltage." Appx2664-2667; *see* Appx2658-2662. But as Dr. Conte admitted, he never even "mention[ed] the RING\_RETENTION\_VOLTAGE" when discussing "how the power mu[ltiplexer] actually operates." Appx2735-2736.

The reason for this omission is clear: RING RETENTION VOLTAGE plays no role in the accused voltage-switching functionality. Instead, Intel's multiplexer switches the C6SRAM's voltage supply from VCCR to VCCIO whenever the chip enters the "Package C7" sleep state. Appx1861-1862 (Intel engineer explaining "[t]here's no relationship" between RING RETENTION VOLTAGE and C6SRAM multiplexer function); Appx1958, Appx2744-2748 (Intel expert showing code for this voltage-switching function does source not mention RING RETENTION VOLTAGE); Appx14187-14209, Appx14210-14223 (source code). Even Dr. Conte *agreed* that Intel's source code causes the multiplexer to switch from VCCR to VCCIO whenever the chip "goes into the [Package] C7, this Appx2669-2670 (describing "package C-State RING C7 entry deep sleep." sequence" in source code and identifying "wire that switches the mu[ltiplexer] when it goes into the package C7").

In denying JMOL, the district court stated that "Dr. Conte demonstrated that RING\_RETENTION\_VOLTAGE acts as the *threshold* for when the voltages are supplied." Appx80-81. However, Dr. Conte merely described examples where either VCCR or VCCIO is supplied to the C6SRAM based on the chip's sleep state. Appx1485; Appx2665-2668; Appx15073; Appx15076. He never showed that RING\_RETENTION\_VOLTAGE is actually used as a "threshold" for determining when VCCR and VCCIO are supplied—because that is not how Intel's products work.

Moreover, the district court and Dr. Conte ignored other examples confirming that Intel's products do the *opposite* of what the "when" limitations require. For instance, VCCR (the alleged "first regulated voltage") is supplied to the C6SRAM at times when it is *below* RING\_RETENTION\_VOLTAGE (i.e., when VCCR is at RING\_VF\_VOLTAGE\_0). *Supra* pp. 27-30. And VCCIO (the accused "second regulated voltage") is supplied to the C6SRAM at times when VCCR is still *at or above* RING\_RETENTION\_VOLTAGE. Appx1862-1863 (Intel engineer explaining that multiplexer switches from VCCR to VCCIO *before* turning VCCR supply off). These examples conclusively demonstrate that Intel's products do not operate as the "when" limitations require.

The district court tried to downplay Dr. Conte's admission that "he did not refer to RING\_RETENTION\_VOLTAGE in describing multiplexer operation" as

"merely introduc[ing] a factual dispute." Appx81; *see* Appx2735-2736. On the contrary, Dr. Conte's admission makes clear there was no factual dispute on this point—all witnesses *agreed* that Intel's products do not actually use RING\_RETENTION\_VOLTAGE (the alleged "minimum operating voltage") in determining "when" to supply which voltage to the C6SRAM. *Supra* p. 34. Yet that is exactly what the plain claim language requires. *Supra* pp. 7-10, 33.

The district court further stated that Dr. Conte "supported his testimony with Intel documents," although it identified no such documents. Appx81. In fact, Intel's documents show that Intel's multiplexer switches the C6SRAM's power supply from VCCR to VCCIO whenever the chip enters the Package C7 sleep state. Appx8830-8831 (Intel specification stating that multiplexer switches when "Vccr is powered down" (i.e., when the chip enters Package C7)); Appx14187-14209, Appx14210-14223 (source code describing Package C7 entry sequence). None of these documents mentions RING\_RETENTION\_VOLTAGE, much less suggests that Intel's multiplexer somehow uses that value in determining "when" to supply VCCR or VCCIO to the C6SRAM.

For these reasons, no reasonable jury could find that Intel's products *literally* satisfy the "when" limitations.

# III. THE INFRINGEMENT JUDGMENT FOR THE '759 PATENT SHOULD BE REVERSED.

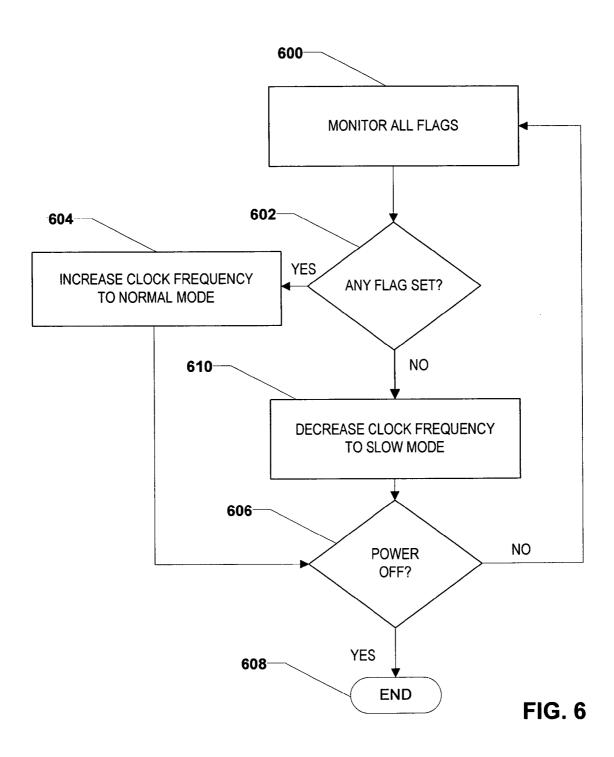

Each asserted claim of the '759 patent requires: (1) a "first master device" that "provide[s]" or "sen[ds]" a "request" to change frequency; and (2) a "clock controller" that "receive[s] the request provided by the first master device[.]" Appx123-124(8:50-9:4, 9:19-40). VLSI's expert Dr. Conte presented an equivalents theory accusing the *combination* of a processor core (the alleged "first master device") and p-code running on the PCU (the alleged "clock controller") of providing the claimed "request" in Intel's products:

Appx15183; *see* Appx2707-2709 ("The claim says 'the first master device provides a request.' Now, it's the first master device *and* its P-code that provides the request."); Appx2708 (testifying that p-code "is running in the PCU"). VLSI's

equivalents theory—which the jury adopted (Appx10)—is barred by prosecution history estoppel and unsupported by substantial evidence.<sup>10</sup>

### A. Prosecution History Estoppel Bars VLSI's Equivalents Theory.

During prosecution, the applicant amended the '759 patent claims to overcome repeated rejections based on the Ansari reference. The proposed claims originally recited that "*at least* one master device" provides a trigger input that includes a "request" to change frequency, and thus allowed multiple components to trigger the request. Appx8044-8045; Appx8237-8238; Appx8273-8274; Appx8316-8317. In four consecutive rejections, the examiner found that Ansari disclosed this "request" limitation and cited functionality performed by two components in Ansari (a master device and an arbiter). Appx8205 (explaining that, in Ansari, the "*[a]rbiter changes the frequency* based on size of transaction," which "is part of trigger input from *master* to *arbiter* to *change the frequency*"); Appx8257; Appx8305-8306; Appx8349; *see* Appx8263; Appx8298-8302; Appx8338-8340; Appx8343-8345; Appx4478-4496.

In response, the applicant attempted to distinguish Ansari by asserting that "[t]he master device does not determine or request a desired bus frequency because *it is the bus arbiter* that determines the bus frequency[.]" Appx8242-8243;

<sup>&</sup>lt;sup>10</sup> For his literal-infringement theory, Dr. Conte alleged that the core alone sends the claimed "request." Appx2691-2695; Appx15153. The jury correctly rejected that theory. Appx9.

Appx8277-8278; Appx8319; Appx8325. After these efforts failed, the applicant canceled all pending claims and rewrote the "request" limitations as demonstrated by the following representative comparison:

| Pre-Amendment Claim 22                        | Post-Amendment Claim 44                                                                     |

|-----------------------------------------------|---------------------------------------------------------------------------------------------|

| 1                                             | <i>a master device</i> coupled to the bus, <i>the master device</i> provide[s] a request to |

| <i>master device</i> provides a corresponding | change the clock frequency in response to a predefined change in                            |

Appx8316-8317; Appx8368; *see* Appx50. Only *after* the applicant narrowed the claims to require that "the master device" (rather than "the *at least* one master device") provide the "request" to change frequency did the examiner withdraw the Ansari-based rejections. Appx8392-8394; Appx8432-8435; Appx8472.

Prosecution history estoppel bars VLSI's attempt to reclaim through equivalents what the applicant surrendered during prosecution. The amendment described above was made for a substantial reason of patentability—namely, to overcome prior-art rejections. *Pioneer Magnetics, Inc. v. Micro Linear Corp.*, 330 F.3d 1352, 1357 (Fed. Cir. 2003). And it was narrowing because the applicant canceled claims that allowed the first master device in combination with other components ("the *at least* one master device") to provide the request to change frequency, and replaced them with claims requiring "the master device" to provide that request. *Supra* pp. 38-39. This narrowing amendment is "presumed" to

disclaim "the territory between the original claim and the amended claim." *Pharma Tech*, 942 F.3d at 1380. VLSI is therefore barred from relying on Dr. Conte's equivalents theory, which alleged that the master device in combination with another component (the PCU) provided the claimed "request." Appx2707-2709.

VLSI cannot rebut the presumption that estoppel applies. First, the alleged equivalent—the master device in combination with another component providing the request to change frequency—was foreseeable because it was disclosed in Ansari and contemplated in the rejected claim language. Second, "an amendment made to avoid prior art that contains the equivalent in question is not tangential[.]" *Festo Corp. v. Shoketsu Kinzoku Kogyo Kabushiki Co.*, 344 F.3d 1359, 1369 (Fed. Cir. 2003) (en banc). Third, there is "no other reason," such as "the shortcomings of language," that "'the [applicant] could not reasonably be expected to have described" the alleged equivalent. *Id.* at 1370.

The district court refused to apply prosecution history estoppel *solely* because it concluded that the amendment described above "did not narrow the claim scope." Appx53; *see* Appx1. That conclusion was wrong, and based on clearly-erroneous factual findings. *See* Appx27-35. The amendment was plainly narrowing because the claims originally allowed multiple components working together to provide the "request," but as amended required "the master device" to do so. *Supra* pp. 38-39; *see Deering Precision Instruments, L.L.C. v. Vector Distrib. Sys., Inc.*, 347 F.3d 1314, 1325-1326 (Fed. Cir. 2003) (applying estoppel where applicant deleted original claims and added other claims with new limitation). And this amendment led the examiner to withdraw the previous Ansari-based rejections, confirming that it was narrowing. *See Laitram Corp. v. NEC Corp.*, 163 F.3d 1342, 1348 (Fed. Cir. 1998) ("[I]t is difficult to conceive of many situations in which the scope of a rejected claim that became allowable when amended is not substantively changed by the amendment[.]").

The district court nonetheless reasoned that the amendment "did not impact the claim scope" because the amended claims recited "*a master device* coupled to the bus, the master device operable to provide a request to change the clock frequency" (Appx8368) and "the indefinite article 'a' means 'at least one." Appx52 (citing *Crystal Semiconductor Corp. v. TriTech Microelectronics Int'l, Inc.*, 246 F.3d 1336, 1347 (Fed. Cir. 2001)). The court further stated that "[w]ithout any reference to 'alone' in any of the claims," it would "not reinterpret the Federal Circuit's instruction that 'a' means 'at least one." Appx52-53.

This Court does not apply such a formalistic approach devoid of context. While "[a]s a general rule, the words 'a' or 'an' in a patent claim carry the meaning of 'one or more,'" "[t]he general rule does *not* apply when the context clearly evidences that the usage is limited to the singular." *TiVo, Inc. v. EchoStar Commc'ns Corp.*, 516 F.3d 1290, 1303-1305 (Fed. Cir. 2008). That is the case here: the amended claim language and prosecution history make clear that "the master device" itself—and not in combination with other components—must provide the claimed "request." *Supra* pp. 38-39; *see, e.g., TiVo*, 516 F.3d at 1303-1305 ("[T]he claims and written description … make clear that the *singular* meaning applies" to term "*an* MPEG stream[.]"); *Philips Elecs. N. Am. Corp. v. Contec Corp.*, 177 F. App'x 981, 987 (Fed. Cir. 2006) (construing "an entry initiate key" to mean "one entry initiate key" where "claim language was amended from '*ones* of said keys' to '*one* of said keys'"). Indeed, had the applicant intended the new claim language reciting "a master device" merely to cover the same scope as the original "at least one master device" language, there would have been no need to amend this language at all.<sup>11</sup>

Given the narrowing amendment made to the "request" limitations, prosecution history estoppel bars VLSI's equivalents theory, which improperly sought to recapture what the applicant surrendered.

# B. The Jury's Infringement Finding Is Unsupported By Substantial Evidence.

To prove infringement by equivalents, VLSI had to present "particularized testimony and linking argument' as to the insubstantiality of the differences between

<sup>&</sup>lt;sup>11</sup> The district court's reference to an "informality" relates to a *later* amendment fixing a "lack[] [of] antecedent basis" by changing one remaining instance of "the at least one master device" to "the master device." Appx53; *see* Appx8385; Appx8405. This later amendment merely conformed language to the earlier amendment; that the examiner described the later amendment as an "informality" does not change the impact of the earlier narrowing amendment.