No. 2021-1709

# United States Court of Appeals for the Federal Circuit

ROHM SEMICONDUCTOR USA, LLC, Plaintiff-Appellant,

v.

MaxPower Semiconductor, Inc., Defendant-Appellee.

Appeal from the United States District Court for the Northern District of California in Case No. 1:20-cv-06686-VC, Judge Vince Chhabria

#### ROHM SEMICONDUCTOR USA, LLC'S OPENING BRIEF

Lisa Kobialka

James Hannah

KRAMER LEVIN NAFTALIS

& FRANKEL LLP

990 Marsh Road

Menlo Park, California 94025

Telephone: (650) 752-1700

Aaron M. Frankel

Cristina Martinez

Shannon H. Hedvat

KRAMER LEVIN NAFTALIS

& FRANKEL LLP

1177 Avenue of the Americas

New York, New York 10036

Telephone: (212) 715-9100

COUNSEL FOR PLAINTIFF-APPELLANT ROHM SEMICONDUCTOR USA, LLC

#### **CERTIFICATE OF INTEREST**

- 1. The full name of every party represented by me is:

- Rohm Semiconductor USA, LLC

- 2. The name of the real party in interest represented by me is:

- Rohm Semiconductor USA, LLC

- Rohm Co., Ltd.

- 3. All parent corporations and any publicly held companies that own 10 percent of the stock of the party or amicus curia represented by me are listed below:

- Rohm USA, Inc.

- Rohm Co., Ltd.

- 4. The names of all law firms, partners and associates that have not entered an appearance in the appeal, and (a) appeared for the entity in the lower tribunal; or (b) are expected to appear for the entity in this court:

- None.

- 5. Other than the originating case numbers(s), the title and number of any case known to counsel to be pending in this or any other court or agency that will directly affect or be directly affected by this court's decision in the pending appeal:

- MaxPower Semiconductor, Inc. v. Rohm Co., Ltd. and Rohm Semiconductor USA, LLC, Case No. 21-cv-375899 (Sup. Ct. Cal. Feb. 10, 2021).

- 6. All information required by Fed. R. App. P. 26.1(b) and (c) in criminal cases and in bankruptcy cases.

- None.

Dated: May 3, 2021 /s/ Lisa Kobialka Lisa Kobialka

#### TABLE OF CONTENTS

|                                                                                                    |       |                                                                                                                                                                            | <u>Page</u> |

|----------------------------------------------------------------------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| CERT                                                                                               | IFICA | ATE OF INTEREST                                                                                                                                                            | i           |

| STATI                                                                                              | EMEN  | NT OF RELATED CASES                                                                                                                                                        | 1           |

| JURIS                                                                                              | DICT  | TIONAL STATEMENT                                                                                                                                                           | 2           |

| STAT                                                                                               | EMEN  | NT OF THE ISSUE ON APPEAL                                                                                                                                                  | 3           |

| STAT                                                                                               | EMEN  | NT OF THE CASE                                                                                                                                                             | 4           |

| STATI                                                                                              | EMEN  | NT OF THE FACTS                                                                                                                                                            | 5           |

| _                                                                                                  | A.    | MaxPower Accused Rohm USA of Patent Infringement                                                                                                                           | 5           |

| ]                                                                                                  | В.    | Rohm Japan and MaxPower Entered Into a Technology License Agreement Thirteen Years Ago                                                                                     | 6           |

| (                                                                                                  | C.    | The Technology License Agreement's Arbitration Provision is Narrow and Limited to Contractual Disputes                                                                     | 6           |

| ]                                                                                                  | D.    | The District Court Granted MaxPower's Motion to Compel Arbitration                                                                                                         | 7           |

| SUMN                                                                                               | //ARY | OF THE ARGUMENT                                                                                                                                                            | 8           |

| ARGU                                                                                               | MEN   | T                                                                                                                                                                          | 10          |

| I. The District Court Erred in Delegating to an Arbitrator the Threshold Question of Arbitrability |       |                                                                                                                                                                            | 10          |

|                                                                                                    | A.    | This Court Applies De Novo Review to the District Court's Dismissal                                                                                                        | 10          |

| ]                                                                                                  | B.    | First Options Requires Courts to Resolve Questions of Arbitrability Themselves Unless the Parties Clearly and Unmistakably Agreed to Delegate That Question to Arbitrators | 11          |

| C.      | The TLA's Reference to California Law is Not a Clear and Unmistakable Agreement to Delegate All Arbitrability Disputes to Arbitrators | 14 |

|---------|---------------------------------------------------------------------------------------------------------------------------------------|----|

| D.      | Oracle and the Other Cases Cited By the District Court Do Not Apply                                                                   | 17 |

| E.      | Oracle Cannot Overturn the Supreme Court's Decision in First Options                                                                  | 21 |

| CONCLUS | SION                                                                                                                                  | 24 |

#### **TABLE OF AUTHORITIES**

| I                                                                                   | Page(s) |

|-------------------------------------------------------------------------------------|---------|

| Federal Cases                                                                       |         |

| AT&T Techs., Inc. v. Communications Workers of Am., 475 U.S. 643 (1986)             | .12, 16 |

| First Options of Chicago, Inc. v. Kaplan, 514 U.S. 938 (1995)                       | passim  |

| French v. Merrill Lynch, Pierce, Fenner & Smith, Inc., 784 F.2d 902 (9th Cir. 1986) | 11      |

| Henry Schein, Inc. v. Archer & White Sales, Inc.,<br>139 S. Ct. 524 (2019)          | 12      |

| Howsam v. Dean Witter Reynolds, Inc., 537 U.S. 79, 86 (2002)                        | 22      |

| Microchip Tech. Inc. v. U.S. Philips Corp.,<br>367 F.3d 1350 (Fed. Cir. 2004)       | 11      |

| Oracle America, Inc. v. Myriad Group A.G.,<br>724 F.3d 1069 (9th Cir. 2013)         | passim  |

| Promega Corp. v. Life Techs. Corp.,<br>674 F.3d 1352 (Fed. Cir. 2012)               | 11      |

| SEIU Local 121RN v. Los Robles Reg'l Med. Ctr.,<br>976 F.3d 849 (9th Cir. 2020)     | 23      |

| Verinata Health Inc. v. Ariosa Diagnostics Inc.,<br>830 F.3d 1335 (Fed. Cir. 2016)  | .10, 11 |

| California Cases                                                                    |         |

| Dream Theater, Inc. v. Dream Theater,<br>124 Cal. App. 4th 547 (2004)               | 18      |

| Gipson v. Davis Realty Co.,<br>215 Cal. App. 2d 190 (Ct. App. 1963)                 | 20      |

| Rhyne v. Mun. Ct.,<br>113 Cal. App. 3d 807 (Ct. App. 1980)                      | 20        |

|---------------------------------------------------------------------------------|-----------|

| Walt Rankin & Assocs., Inc. v. City of Murrieta,<br>84 Cal. App. 4th 605 (2000) | 19        |

| Other State Cases                                                               |           |

| Doe v. Natt,<br>299 So. 3d 599 (Fla. Dist. Ct. App. 2020)                       | 22        |

| California Statutes                                                             |           |

| Cal. Civ. Proc. Code § 1281.2                                                   | 9 15 20   |

| § 1281.3                                                                        | 19        |

| § 1297.161                                                                      | 8, 15, 19 |

| § 1297.191                                                                      | 19        |

|                                                                                 |           |

#### **STATEMENT OF RELATED CASES**

Pursuant to Fed. Cir. Rule 47.5, Appellant Rohm Semiconductor USA, LLC ("Rohm USA"), states that:

- 1) The following appeals have been taken from the following lower courts or bodies:

- None.

- 2) Appellant Rohm USA is a party to the following additional cases, which may be directly affected by the Court's decision in this appeal:

- MaxPower Semiconductor, Inc. v. Rohm Co., Ltd. and Rohm Semiconductor USA, LLC, Case No. 21-cv-375899 (Sup. Ct. Cal. Feb. 10, 2021).

#### **JURISDICTIONAL STATEMENT**

The District Court had jurisdiction over this action under 28 U.S.C. §1331 and §1338 because this action arose under the Patent Act of 35 U.S.C. § 101 *et seq*.

The District Court dismissed this action in favor of Defendant-Appellee MaxPower Semiconductor, Inc. ("MaxPower") on February 4, 2021. Appx1-2.

Rohm USA timely filed a notice of appeal pursuant to Federal Rule of Appellate Procedure 4(a)(2) on February 23, 2021. Appx853-854.

This Court has jurisdiction under 28 U.S.C. § 1295(a).

#### **STATEMENT OF THE ISSUE ON APPEAL**

1. Whether the District Court erred in concluding that the parties' agreement to arbitrate "in accordance with the provisions of the California Code of Civil Procedure" represented a "clear and unmistakable" agreement to have an arbitrator decide questions of arbitrability instead of a court?

#### **STATEMENT OF THE CASE**

Rohm USA filed suit against MaxPower seeking a declaration that Rohm USA does not infringe U.S. Patent Nos. 7,843,004, 8,076,719, 8,466,025, and 8,659,076 (together, the "MaxPower Patents"). *Rohm Semiconductor USA, LLC v. MaxPower Semiconductor, Inc.*, Case No. 20-cv-06686-VC (N.D. Cal. Sep. 23, 2020 (the "DJ Action"); Appx156-163. The DJ Action was ultimately assigned to Judge Vince Chhabria (the "District Court") of the United States District Court for the District of Northern California.

MaxPower filed a Second Renewed Motion to Compel Arbitration and Stay Claims for Declaratory Judgment (the "Motion to Compel"), contending that Rohm USA's request for a declaration of non-infringement was subject to arbitration. Appx708-725. The District Court granted MaxPower's Motion to Compel on February 4, 2021, and dismissed the DJ Action without prejudice. Appx1-2. The District Court did not make any finding on the ultimate question of the arbitrability of Rohm USA's claim, but found that the question of arbitrability must be resolved by an arbitrator. *Id*.

Rohm USA timely filed a notice of appeal on February 23, 2021. Appx853-854.

#### **STATEMENT OF THE FACTS**

#### A. MaxPower Accused Rohm USA of Patent Infringement

Appellant Rohm USA sells a variety of products, including silicon carbide metal oxide semiconductor field effect transistors ("SiC MOSFETs"). Appx158 at ¶¶ 9-10, 12. Rohm USA's SiC MOSFETs are used to control the flow of electrical current in electronic devices, and were developed with leading-edge technology to provide superior performance in high-voltage applications. *Id.* Non-party Rohm Co., Ltd. ("Rohm Japan"), Rohm USA's ultimate corporate parent, developed Rohm USA's SiC MOSFETs. Appx315-316; Appx158 at ¶ 12.

MaxPower accused Rohm USA of infringing the four MaxPower Patents based on Rohm USA's sales in the United States of SiC MOSFETs. Appx157-159 ¶¶ 1, 13. Rohm USA denies that its SiC MOSFETs infringe any of the MaxPower Patents. Rohm USA filed the underlying declaratory judgment action to obtain a declaration of non-infringement and to clear the cloud of MaxPower's infringement allegations. Appx157 at ¶¶ 1-3.

Rohm USA also filed petitions for *inter partes* review against each of the four MaxPower Patents. As these petitions are not at issue in this appeal, they will not be further discussed herein.

## B. Rohm Japan and MaxPower Entered Into a Technology License Agreement Thirteen Years Ago

In 2007, Rohm Japan and MaxPower entered into a Technology License Agreement, which was subsequently amended various times. Appx651-664 (the "TLA"). Under the TLA, MaxPower agreed to provide Rohm Japan with certain limited and now-obsolete disclosures in exchange for Rohm Japan's payment of royalties on products developed based on those disclosures, specifically silicon MOSFETs. Appx651-655 (TLA at §§ 1.2, 1.8, 4); Appx635-644 at Appx646.

The TLA does not cover SiC MOSFETs and MaxPower never provided SiC MOSFET plans, designs, or technology to Rohm Japan during the course of either agreement. *See*, *e.g.*, Appx646 (2007 Target Specification). In addition, under the TLA, Rohm Japan does not have any royalty obligations for any independently developed technology — that is, any developments without the use of MaxPower's technology disclosed under the TLA. Appx652 (TLA at § 1.8).

## C. The Technology License Agreement's Arbitration Provision is Narrow and Limited to Contractual Disputes

While Rohm Japan and MaxPower agreed to arbitrate disputes "arising out of or in relation" to the TLA, they did not agree to arbitrate any other disputes, such as patent disputes:

<u>Arbitration</u>: Any dispute, controversy, or claim *arising* out of or in relation to this Agreement or at law, or the breach, termination or invalidity thereof, that cannot be settled amicably by agreement of the parties hereto, shall

be finally settled by arbitration in Santa Clara County, California, USA in accordance with the provisions of the California Code of Civil Procedure by one or more arbitrators appointed in accordance with said Code . . .

Appx672-678 (2<sup>nd</sup> Amend. TLA at ¶ 10) (amending § 13.6 of the TLA) (emphasis added).

Notably, the TLA's arbitration provision does not reference arbitrating disputes of patent infringement issues. The TLA is also silent as to the question of who should decide any disputes over arbitrability.

### D. The District Court Granted MaxPower's Motion to Compel Arbitration

In lieu of answering Rohm USA's declaratory judgment complaint, MaxPower filed a first motion to compel arbitration, which the District Court dismissed on procedural grounds not at issue on appeal. Appx497-498; Appx567-568. MaxPower filed a renewed motion to compel, which it then withdrew to file the Motion to Compel now on appeal. Appx679-680; Appx704-705; Appx706-707; Appx708-725; Appx753-767; Appx834-846. The premise of MaxPower's Motion to Compel is MaxPower's allegation that the parties specifically agreed to arbitrate Rohm USA's claim for a declaration of non-infringement.

The District Court issued a one paragraph order granting MaxPower's Motion to Compel (the "Order"). Appx1-2. The District Court made no finding on the question of if the parties had agreed to arbitrate requests for a declaration of patent

non-infringement. Instead, the District Court found that this threshold question of arbitrability should be decided by an arbitrator and not by the District Court. *Id*.

The District Court noted that, "[t]he TLA incorporates the California Code of Civil Procedure [("CCCP")] into its arbitration provision." *Id.* The District Court then quoted the CCCP's add on provisions for international arbitration which state that "[t]he arbitral tribunal *may* rule on its own jurisdiction." *Id.* (emphasis added) (quoting Cal. Civ. Proc. Code § 1297.161). The District Court found this reference to the CCCP to have "clearly and unmistakably delegate[d] the question of arbitrability to the arbitrator," and dismissed the DJ Action. The District Court did not identify, nor did MaxPower offer, any other evidence of an agreement to delegate arbitrability to an arbitrator. *Id.*

#### **SUMMARY OF THE ARGUMENT**

The District Court erred in dismissing the DJ Action because the parties never "clearly and unmistakably" agreed to have an arbitrator decide disputes over arbitrability.

Under the Supreme Court's controlling *First Options* decision, in the absence of such a clear and unmistakable agreement, questions of arbitrability are reserved to the courts. *First Options of Chicago, Inc. v. Kaplan*, 514 U.S. 938, 944-45 (1995). Such a "clear and unmistakable delegation" would usually consist of an express statement in the arbitration provision agreeing to arbitrate any questions of

arbitrability. Here, in contrast, the parties' agreement is completely silent on the issue of who decides questions of arbitrability. Thus, because there was no clear and unmistakable delegation of arbitrability, the District Court should have itself decided the threshold question of arbitrability. For this reason, reversal and remand are warranted.

In *First Options*, the Supreme Court recognized the fundamental unfairness in having arbitrators decide questions of arbitrability, when arbitrators have every incentive to determine that a dispute is subject to arbitration. To prevent parties from being forced to arbitrate disputes they never agreed to arbitrate, the courts (not arbitrators) are supposed to be the gatekeepers of arbitrability unless the parties expressly agree to the contrary. *See id.*

In finding that Rohm USA had clearly and unmistakably agreed to have only an arbitrator decide arbitrability disputes, the District Court erroneously relied on the Ninth Circuit's decision in *Oracle America, Inc. v. Myriad Group A.G.*, 724 F.3d 1069 (9th Cir. 2013). In *Oracle*, the incorporation of UNCITRAL's rules was deemed an agreement to delegate arbitrability disputes to an arbitrator. Indeed, the UNCITRAL rules provided for arbitrators to decide arbitrability questions. Here, in contrast, the parties' agreement references the CCCP. The CCCP expressly provides that *courts* may decide questions of arbitrability, while also permitting arbitrators to decide such questions in limited circumstances. *See* CCCP § 1281.2. Thus,

incorporation of the CCCP is not a clear and unmistakable agreement to delegate arbitrability.

For this reason, *Oracle* does not apply here. But to the extent *Oracle would* require an arbitrator to decide arbitrability under these facts, it must be set aside as contrary to the Supreme Court's *First Options* decision. *Oracle* and its progeny cannot abrogate the Supreme Court's requirement that arbitrability questions can only be delegated to an arbitrator if there is a clear and unmistakable agreement to do so. Indeed, during oral argument, the District Court acknowledged that *Oracle* is inconsistent with the clear and unmistakable standard, acknowledging that "one could say that clear and unmistakable is no longer clear and unmistakable after *Oracle*." Appx887-889 at 9:6-16.

MaxPower is seeking to force an unwilling party to arbitrate an issue that was never contemplated under the TLA. Reversal is warranted under *First Options* so that the District Court may decide the threshold question of arbitrability.

#### **ARGUMENT**

- I. The District Court Erred in Delegating to an Arbitrator the Threshold Question of Arbitrability

- A. This Court Applies De Novo Review to the District Court's Dismissal

This Court applies de novo review to the District Court's dismissal of the DJ Action. *Verinata Health Inc. v. Ariosa Diagnostics Inc.*, 830 F.3d 1335, 1338 (Fed. Cir. 2016).

As the regional circuit, Ninth Circuit law applies. *Microchip Tech. Inc. v. U.S. Philips Corp.*, 367 F.3d 1350, 1356 (Fed. Cir. 2004) ("We are obligated to follow regional circuit law on questions of arbitrability that are not 'intimately involved in the substance of enforcement of a patent right."") (citation omitted).

The District Court did not make any underlying factual determinations in support of its Order, which would have been subject to "clear error" review.

\*Verinata Health\*, 830 F.3d at 1338 (citing \*Promega Corp. v. Life Techs. Corp., 674 F.3d 1352, 1355 (Fed. Cir. 2012)). Specifically, the District Court's interpretation of the scope of the TLA's arbitration provision, which did not rest on any extrinsic evidence, is a question of law to which de novo review is applied. \*See French v. Merrill Lynch, Pierce, Fenner & Smith, Inc., 784 F.2d 902, 908 (9th Cir. 1986).

B. First Options Requires Courts to Resolve Questions of Arbitrability Themselves Unless the Parties Clearly and Unmistakably Agreed to Delegate That Question to Arbitrators

The Supreme Court dictated that the courts, not arbitrators, should be the gatekeepers to decide if a dispute is subject to arbitration, unless the parties have a clear and unmistakable agreement to the contrary. Here, the District Court erred in finding that only an arbitrator should decide the threshold question of arbitrability because Rohm and MaxPower never expressly agreed to send arbitrability questions to an arbitrator.

In *First Options*, 514 U.S. 938 at 944, the Supreme Court held that courts should decide arbitrability questions and should *not* "assume that the parties agreed to arbitrate arbitrability unless there is 'clea[r] and unmistakabl[e]' evidence that they did so." *Id.* at 944 (citations omitted); *see Henry Schein, Inc. v. Archer & White Sales, Inc.*, 139 S. Ct. 524, 531 (2019) ("courts 'should not assume that the parties agreed to arbitrate arbitrability unless there is a clear and unmistakable evidence that they did so"); *see also AT&T Techs., Inc. v. Communications Workers of Am.*, 475 U.S. 643, 649 (1986) ("Unless the parties clearly and unmistakably provide otherwise, the question of whether the parties agreed to arbitrate is to be decided by the court, not the arbitrator."). Here, as discussed in the following section, Rohm never agreed to delegate arbitrability, so it was legal error for the District Court to not itself decide the issue.

The Supreme Court set forth a basic presumption in favor of having courts decide if a dispute is arbitrable. When there is "silence or ambiguity about the question 'who . . . should decide arbitrability," as is the case here, the courts must do so themselves. *First Options*, 514 U.S. at 944-45 (emphasis in original) (citation omitted). This is because the general presumption in favor of arbitration does not apply to the question of who should decide a dispute over arbitrability. *Id.* Thus, under *First Options*, if a contract includes an arbitration provision, it will be interpreted to require courts to decide questions of arbitrability, unless the

parties have a clear and unmistakable agreement to delegate that question to arbitrators.

The Supreme Court explained the policy behind this presumption against delegation of arbitrability to be a matter of fundamental fairness, given the "arcane" nature of the question and the likelihood that parties did not focus on it in negotiating their arbitration provision:

the "who (primarily) should decide arbitrability" question—is rather arcane. A party often might not focus upon that question or upon the significance of having arbitrators decide the scope of their own powers.

First Options, 514 U.S. at 945 (citations omitted).

The Supreme Court further recognized the risk of giving arbitrators the power to decide if a dispute is subject to arbitration, given the incentive that arbitrators have to find in favor of arbitrability, causing parties such as Rohm USA to arbitrate disputes they never agreed to arbitrate:

[G]iven the principle that a party can be forced to arbitrate only those issues it specifically has agreed to submit to arbitration, one can understand why courts might hesitate to interpret silence or ambiguity on the "who should decide arbitrability" point as giving the arbitrators that power, for doing so might too often *force unwilling parties to arbitrate a matter they reasonably would have thought a judge, not an arbitrator, would decide*.

*Id.* (citations omitted) (emphasis added).

Thus, the District Court was to presume that Rohm USA did not agree to delegate arbitrability questions, and should have decided the question itself

because there is no clear and unmistakable agreement between Rohm and MaxPower to only allow arbitrators to decide that question.

## C. The TLA's Reference to California Law is Not a Clear and Unmistakable Agreement to Delegate All Arbitrability Disputes to Arbitrators

The District Court erred in dismissing the DJ Action because the TLA does not include a clear and unmistakable agreement to exclusively delegate arbitrability disputes to arbitrators. To the contrary, it is entirely silent on the issue of who will decide questions of arbitrability. Appx677-678 (2<sup>nd</sup> Amend. TLA at § 10). Such silence cannot be a clear and unmistakable agreement to delegate arbitrability questions. Therefore, applying de novo review, the Court should reverse under *First Options*.

The only purported evidence offered by MaxPower of an agreement to delegate arbitrability, and the sole basis relied upon by the District Court, was the statement in the TLA's arbitration provision that "Any . . . claim arising out of or in relation to this Agreement . . . shall be finally settled by arbitration . . . in accordance with the provisions of the California Code of Civil Procedure [CCCP]." Appx1-2; Appx718-720; Appx840-841.

The District Court, applying the Ninth Circuit's *Oracle* decision (discussed in the following section), erroneously found that this single, generic reference to the CCCP was a "clear and unmistakable" agreement to have arbitrators — but not

courts — resolve arbitrability disputes because the CCCP's international arbitration subsection provides that an "arbitral tribunal *may* rule on its own jurisdiction." Appx1 (citing Cal. Civ. Proc. Code § 1297.161) (emphasis added).

The error in the District Court's analysis is that the CCCP does *not* require arbitrators to decide all questions of arbitrability, so a reference to the CCCP is not equivalent to an agreement to arbitrate arbitrability disputes. In particular, the CCCP's arbitration provisions expressly provide that *courts* should decide questions of arbitrability, providing a specific procedure for the resolution of such disputes: "the *court* shall order the petitioner and the respondent to arbitrate the controversy *if it determines that an agreement to arbitrate the controversy exists.*" CCCP § 1281.2 (emphasis added). This general provision applies to all arbitrations under the CCCP. *Id.*

The provision of the CCCP upon which the District Court relied, § 1297.161, is permissive in permitting international arbitrators to resolve questions of arbitrability, but does not negate the courts' statutory authority under the CCCP to also determine questions of arbitrability. *See* CCCP § 1297.161. Thus, the most that can be said about the CCCP on this issue is that a court is always empowered to decide questions of arbitrability and, for international arbitrations, an arbitral tribunal may also decide such questions. Given that the CCCP does not exclusively delegate to arbitrators questions of arbitrability, a

reference to the CCCP, without more, is not a clear agreement to have only arbitrators decide arbitrability.

This should have ended the inquiry for the District Court in this case because the incorporation of the CCCP into the TLA cannot have been the result of a "clear and unmistakable" agreement to strip courts of the statutory ability to resolve arbitrability, and, therefore, "the question of whether the parties agreed to arbitrate [wa]s to be decided by the [C]ourt." *AT&T Techs.*, 475 U.S. at 649.

For the District Court to find otherwise, it had to find that, when the parties negotiated the TLA and its arbitration provision in 2007, they specifically agreed that if they later disagreed on an arbitrability question that they would take that question away from the courts and have it be decided only by an arbitrator. The District Court would further need to find that, in order to record the agreement, the parties specifically chose to incorporate the CCCP as a shorthand for expressly stating that they intended to have only arbitrators decide arbitrability. Moreover, the District Court would need to find that the parties appreciated the "arcane" nuances of the multiple provisions in the CCCP that permit both courts and arbitrators to decide questions of arbitrability and, yet, assumed that incorporation of the CCCP would be sufficiently clear to reflect their otherwise unexpressed agreement to delegate arbitrability questions.

The District Court made no such findings. Nor could it have. To the contrary, the District Court recognized that applying *Oracle* here effectively ignored the *First Options* clear and unmistakable standard and that there was no clear and unmistakable agreement here. Appx887-889 at 9:6-16. Reading an agreement to delegate arbitrability disputes into the TLA where none exists is legal error and does not reflect an actual agreement between the parties on this issue. Therefore, under *First Options*, the District Court erred in granting MaxPower's Motion to Compel in the absence of such evidence.

## D. Oracle and the Other Cases Cited By the District Court Do Not Apply

In erroneously finding that the parties agreed to arbitrate the question of arbitrability, the District Court relied on the Ninth Circuit's *Oracle* decision and several similar cases. Those cases are distinguishable because of the differences in the parties' agreements they considered. In those cases, unlike this case, the parties agreed to arbitrate under the rules of a specific organization that *only* permitted arbitrators to decide arbitrability questions. The arbitration rules incorporated into the agreements in those cases did not include a provision equivalent to the CCCP's provision providing for *courts* to decide arbitrability disputes.

For example, in *Oracle America, Inc. v. Myriad Group A.G.*, 724 F.3d 1069 (9th Cir. 2013), upon which the District Court relied, the agreement at issue

incorporated UNCITRAL rules which *expressly* "delegate[] questions of arbitrability" to an arbitrator. *Id.* at 1073. Similarly, in *Dream Theater, Inc. v. Dream Theater*, 124 Cal. App. 4th 547 (2004), also cited in the Order, the court held that the "[AAA Commercial Arbitration Rules] . . . *specify* that the arbitrator will decide disputes over the scope of the arbitration agreement," deeming the incorporation of AAA rules to, therefore, be an unmistakable agree to delegate arbitrability to arbitrators. *Id.* at 557 (emphasis added). None of the rules incorporated into the arbitration provisions in these cases relied upon by the District Court expressly provide for courts to resolve questions of arbitrability, as the CCCP does.

An additional reason *Oracle* and the other cases are distinguishable is that the arbitration agreements in those cases incorporated a specific set of rules which, those courts reasoned, was an unmistakable agreement to incorporate the delegation of arbitrability unambiguously provided by those rules. *See*, *e.g.*, *Oracle*, 724 F.3d at 1074 (expressly incorporating UNCITRAL rules which is "consistent with the majority view regarding the effect of incorporating the AAA rules into an agreement").

Here, in contrast, the TLA's reference to the entirety of the CCCP's sprawling arbitration provisions, sweeps in general arbitration provisions, as well as a variety of rules that apply in different circumstances, such as the consolidation

of separate arbitration proceedings, the selection of the procedure to be followed by an arbitral tribunal to conduct the proceedings, and international arbitration.

See CCCP at e.g., §§ 1281.3, 1297.191, 1297.161. The TLA did not limit its incorporation of the CCCP to any particular subsections and, in particular, did not expressly provide for arbitration specifically under the international arbitration provisions that MaxPower relies on. Appx677-678 (2<sup>nd</sup> Amend. TLA at § 10).

Therefore, general reference to the CCCP is not a clear an unmistakable reference to the specific arbitrability provision of the international sub-section of the CCCP. This is especially the case here, where the underlying case is a domestic dispute between Rohm USA and MaxPower — both California entities, for a declaratory judgment of non-infringement of MaxPower's United States patents relating to Rohm USA's sales of SiC MOSFETs in the United States. Appx157 at ¶¶ 1-3.

Even if the dispute between Rohm USA and MaxPower were interpreted to be an international one, CCCP § 1297.161 simply sets forth that an international arbitral tribunal "may rule on its own jurisdiction," not that it must or exclusively can do so. CCCP § 1297.161 (emphasis added). California courts have held that may has a specific legal meaning (in contrast to shall), writing that "the usual rule with California codes is that 'shall' is mandatory and 'may' is permissive unless the context requires otherwise." *Walt Rankin & Assocs., Inc. v. City of Murrieta*, 84 Cal. App. 4th 605, 614 (2000) (citation omitted).

This distinction between "shall" and "may" extends to the CCCP, as courts interpreting sections of the CCCP have held that, "in the absence of such special circumstances, ["may"] should be interpreted as permissive or conferring discretion." *Rhyne v. Mun. Ct.*, 113 Cal. App. 3d 807, 817 (Ct. App. 1980); *see also Gipson v. Davis Realty Co.*, 215 Cal. App. 2d 190, 202 (Ct. App. 1963) (holding that "may" "is primarily and ordinarily a permissive term").

The permissive and non-exclusive nature of the statement that, in international cases, an arbitrator "may" rule on arbitrability, is confirmed by other provisions in the CCCP providing that the courts may also decide this question.

CCCP § 1281.2 (authorizing court to "determine[] that a written agreement to arbitrate a controversy exists").

The District Court, therefore, was *not* precluded by the CCCP from resolving the issue of arbitrability. The permissive language of the CCCP, solely pertaining to a small subset of disputes (that is, international ones), contrasts with the provisions at issue in the cases the District Court relied upon, which incorporate rules expressly delegating arbitrability. Appx 1. Therefore, the general reference to the CCCP is not a clear and unmistakable agreement to have only arbitrators decide arbitrability questions.

The premise that incorporation of rules for arbitration (especially rules that are ambiguous on arbitrability) is sufficient to delegate arbitrability violates the

public policy embedded in *First Options* that parties should be presumed not to have agreed to delegate arbitrability. First Options, 514 U.S. at 944-45. When Rohm Japan and MaxPower incorporated the CCCP, there is no reason to believe that they actually had in mind this "arcane" issue of the delegation of arbitrability and that they appreciated the interplay of various provisions among the voluminous CCCP that might relate to this issue. *Id.* at 945 ("[a] party often might not focus upon that question or upon the significance of having arbitrators decide the scope of their own powers . . . [thus] one can understand why courts might hesitate to interpret silence or ambiguity on the 'who should decide arbitrability' point as giving the arbitrators that power, for doing so might too often force unwilling parties to arbitrate a matter they reasonably would have thought a judge, not an arbitrator, would decide") (citations omitted). And, if Rohm and MaxPower truly did have a meeting of the mind on this issue, they would have said so expressly in the TLA, not indirectly and ambiguously through reference to the CCCP. Thus, the incorporation of the CCCP was not a clear and unmistakable agreement that only arbitrators should decide arbitrability.

## E. Oracle Cannot Overturn the Supreme Court's Decision in First Options

As discussed above, *First Options* dictates reversal, and the Ninth Circuit's *Oracle* case is not to the contrary because it is distinguishable. Courts have recognized that while "a question over arbitrability [and] who should decide the

answer—the arbitrator or the court—can pose something of an analytical challenge," the *Supreme Court* has "provided a framework to resolve that first order issue in *First Options*." *Doe v. Natt*, 299 So. 3d 599, 602 (Fla. Dist. Ct. App. 2020). And that controlling framework must be applied in every instance, including here.

To the extent *Oracle* dictates a different result under these facts, it must be set aside as inconsistent with the Supreme Court's controlling *First Options* decision. It is pure legal fiction to read the parties' incorporation of the CCCP into the TLA to reflect a negotiated agreement between the parties expressly intended to waive having courts decide arbitrability questions. This fiction cannot be reconciled with *First Options*.

At least one court has criticized *Oracle* as contrary to *First Options* for this reason. In a state court decision declining to find that incorporation of AAA arbitration rules is a clear and unmistakable delegation of arbitrability, *Doe* recognizes that, in *Oracle*, the Ninth Circuit failed to "examine[] how or why the mere 'incorporation' of an arbitration rule . . . satisfied the heightened standard the Supreme Court set in *First Options*, nor how it overcomes the 'strong pro-court presumption' that is supposed to attend this inquiry." *Doe*, 299 So. 3d at 608 (citing *Howsam v. Dean Witter Reynolds, Inc.*, 537 U.S. 79, 86 (2002)).

The District Court here also acknowledged the inconsistency between Oracle and First Options during oral argument, but took the view that its hands were tied and it was obligated to follow Oracle notwithstanding this inconsistency:

I think one could say that clear and unmistakable is no longer clear and unmistakable after Oracle and all of the cases that — all of the other cases that said that you delegate that to the arbitrator, with language like that. . . It's not even in the contract, but it's incorporated in the rules. The language itself is not super specific. I mean I think it is fair to say that clear and unmistakable is no longer just clear and unmistakable, but that's the case law and I'm just not sure how you can get around that.

Appx888 at 9:7-16 (emphasis added).

In following *Oracle*, not the Supreme Court's controlling *First Options* decision, the District Court failed to heed the Ninth Circuit's recent acknowledgment that its own decisions cannot be inconsistent with *First Options*. *See SEIU Local 121RN v. Los Robles Reg'l Med. Ctr.*, 976 F.3d 849, 861 (9th Cir. 2020). In *SEIU Local*, the Ninth Circuit reversed prior Ninth Circuit precedent finding a presumption in favor of delegation of arbitrability in labor cases because those cases were inconsistent with *First Options*' general presumption against delegation. *Id.* ("[a]s *First Options* instructs us, '[c]ourts should not assume that the parties agreed to arbitrate arbitrability' in the face of 'silence or ambiguity' with respect to the Delegation Question' (emphasis added) (citing *First Options*, 514 U.S. at 944-45)). Here, to the extent *Oracle* applies to the TLA's reference to

Case: 21-1709 Document: 10 Page: 30 Filed: 05/03/2021

the CCCP's arbitration rules, which are at most ambiguous as to the question of delegation, it cannot stand in view of First Options.

Thus, under de novo review, the Court should find that First Options applies and, due to the absence of a "clear and unmistakable" agreement to delegate arbitrability, the Order should be reversed.

#### **CONCLUSION**

For the foregoing reasons, Rohm USA respectfully requests that this Court reverse the District Court's grant of the Motion to Compel, and remand this matter to the District Court to decide the question of the arbitrability of Rohm USA's request for a declaration of non-infringement.

#### Respectfully submitted,

Dated: May 3, 2021 By: /s/ Lisa Kobialka

> Lisa Kobialka James Hannah Kramer Levin Naftalis & Frankel LLP 990 Marsh Road Menlo Park, CA 94025

Tel: 650.752.1700 Fax: 650.752.1810

lkobialka@kramerlevin.com jhannah@kramerlevin.com

Aaron M. Frankel Cristina Martinez Shannon H. Hedvat Kramer Levin Naftalis & Frankel LLP

> 1177 Avenue of the Americas New York, NY 10036 Tel: 212.715.9100 Fax: 212.715.8000 afrankel@kramrelevin.com cmartinez@kramerlevin.com shedvat@kramerlevin.com

Attorneys for Plaintiff-Appellant Rohm Semiconductor USA, LLC

#### **CERTIFICATE OF COMPLIANCE**

- 1. This brief complies with the type-volume limitation of Fed. Cir. R. 32(b) because this brief contains 4,792 words, exclusive of the certificate of interest, table of contents, table of citations, statement of related cases, addendum and this certificate of compliance as exempted by Fed. R. App. 32(f) and Fed. Cir. R. 32(b)(2).

- 2. This brief complies with the typeface requirements of Fed. R. App. P. 32(a)(5) and the type style requirements of Fed. R. App. P. 32(a)(6) because this brief has been prepared in a proportionally-spaced typeface using Microsoft Word 2010 in Times New Roman 14-point font.

/s/ Lisa Kobialka Lisa Kobialka

#### **ADDENDUM**

| Date       | Description                                 | Appx No. |

|------------|---------------------------------------------|----------|

| 02/04/2021 | Order Granting Motion to Compel Arbitration | Appx1    |

|            | U.S. Patent No. 7,843,004 (the '004 Patent) | Appx3    |

|            | U.S. Patent No. 8,076,719 (the '719 Patent) | Appx39   |

|            | U.S. Patent No. 8,466,025 (the '025 Patent) | Appx74   |

|            | U.S. Patent No. 8,659,076 (the '076 Patent) | Appx110  |

Case 3:20-cv-06686-VC Document 60 Filed 02/04/21 Page 1 of 2

## UNITED STATES DISTRICT COURT NORTHERN DISTRICT OF CALIFORNIA

ROHM SEMICONDUCTOR USA, LLC, Plaintiff,

v.

MAXPOWER SEMICONDUCTOR, INC.,

Defendant.

Case No. 20-cv-06686-VC

ORDER GRANTING MOTION TO COMPEL ARBITRATION

Re: Dkt. No. 41

MaxPower's motion to compel arbitration is granted. MaxPower's and Rohm Co.'s Technology License Agreement (TLA) binds Rohm Co.'s subsidiaries, including Rohm USA. The TLA incorporates the California Code of Civil Procedure into its arbitration provision. The applicable section provides: "The arbitral tribunal may rule on its own jurisdiction, including ruling on any objections with respect to the existence or validity of the arbitration agreement . . . ." Cal. Civ. Proc. Code § 1297.161. That type of language has repeatedly been held to clearly and unmistakably delegate the question of arbitrability to the arbitrator. *See Oracle America, Inc. v. Myriad Group A.G.*, 724 F.3d 1069 (9th Cir. 2013); *Loewen v. McDonnell*, 403 F. Supp. 3d 832 (N.D. Cal. 2019); *Dream Theater, Inc. v. Dream Theater*, 124 Cal. App. 4th 547 (2004); *see also Henry Schein, Inc. v. Archer and White Sales, Inc.*, 139 S. Ct. 524 (2019). MaxPower's motion is thus granted, and the case is dismissed without prejudice. *See Johnmohammadi v. Bloomingdale's, Inc.*, 755 F.3d 1072, 1073-74 (9th Cir. 2014).

<sup>&</sup>lt;sup>1</sup> MaxPower's motion to seal, filed in conjunction with its motion to compel, is also granted. *See* Docket No. 42.

Case 3:20-cv-06686-VC Document 60 Filed 02/04/21 Page 2 of 2

IT IS SO ORDERED.

Dated: February 4, 2021

VINCE CHHABRIA United States District Judge Case: 21-1709 Document: 10 Page: 36 Filed: 05/03/2021

#### (12) United States Patent Darwish

US 7,843,004 B2 (10) **Patent No.:** (45) Date of Patent: Nov. 30, 2010

| (54) | POWER MOSFET WITH RECESSED FIELD PLATE |                                                                                                                |  |  |

|------|----------------------------------------|----------------------------------------------------------------------------------------------------------------|--|--|

| (75) | Inventor:                              | <b>Mohamed N. Darwish</b> , Campbell, CA (US)                                                                  |  |  |

| (73) | Assignee:                              | <b>MaxPower Semiconductor Inc.</b> , Santa Clara, CA (US)                                                      |  |  |

| (*)  | Notice:                                | Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 388 days. |  |  |

| (21) | Appl. No.:                             | 11/903,972                                                                                                     |  |  |

(22)Filed: Sep. 25, 2007

(65)**Prior Publication Data**

> US 2008/0073707 A1 Mar. 27, 2008

#### Related U.S. Application Data

- (60)Provisional application No. 60/847,551, filed on Sep. 27, 2006.

- (51) Int. Cl. H01L 29/66 (2006.01)

- **U.S. Cl.** ...... **257/341**; 257/329; 257/E29.131; (52)257/E29.183; 257/E29.189; 370/466

- Field of Classification Search ...... 257/328, 257/330, E29.131, E29.183, E29.189, E29.201, 257/E29.257; 370/466

See application file for complete search history.

#### (56)References Cited

U.S. PATENT DOCUMENTS

5,879,980 A 3/1999 Selcuk et al. ...... 438/238

| 5,907,776    | A   | 5/1999  | Hshieh et al.           |

|--------------|-----|---------|-------------------------|

| 6,388,286    | B1  | 5/2002  | Baliga 257/330          |

| 6,429,481    | B1  | 8/2002  | Mo et al.               |

| 6,521,497    | B2  | 2/2003  | Mo                      |

| 6,710,403    | B2  | 3/2004  | Sapp                    |

| 6,710,406    | B2  | 3/2004  | Mo et al.               |

| 6,828,195    | B2  | 12/2004 | Mo et al.               |

| 6,833,584    | B2  | 12/2004 | Henninger et al 257/334 |

| 2005/0167742 | A1* | 8/2005  | Challa et al 257/328    |

| 2005/0208722 | A1  | 9/2005  | Peake et al 438/259     |

| 2006/0060916 | A1* | 3/2006  | Girdhar et al 257/330   |

| 2006/0209887 | A1* | 9/2006  | Bhalla et al 370/466    |

\* cited by examiner

Primary Examiner—Kenneth A Parker Assistant Examiner—Fang-Xing Jiang (74) Attorney, Agent, or Firm—Groover & Associates

#### (57)ABSTRACT

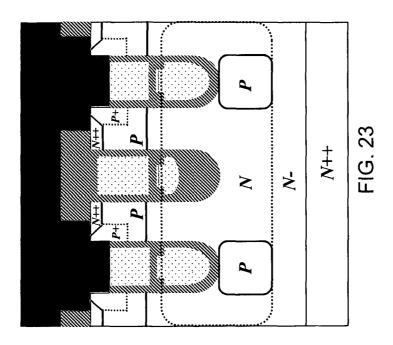

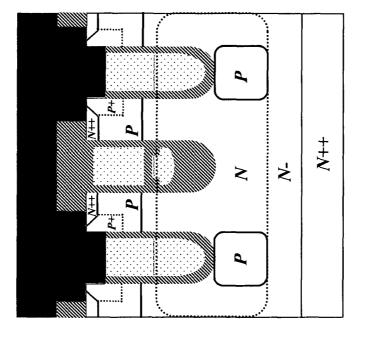

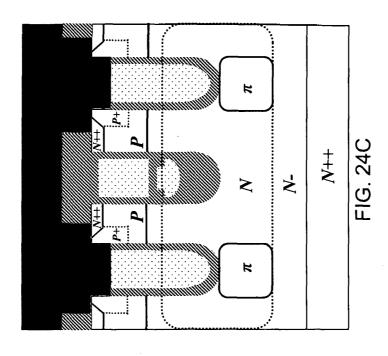

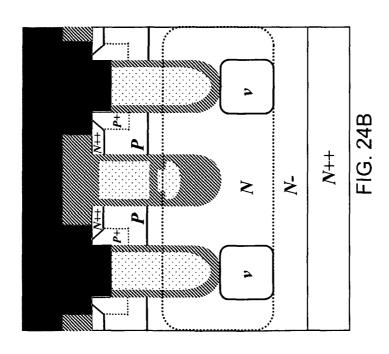

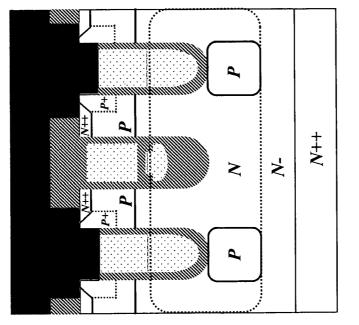

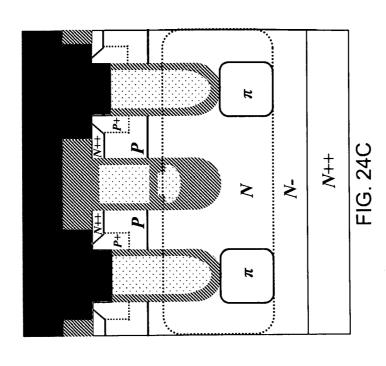

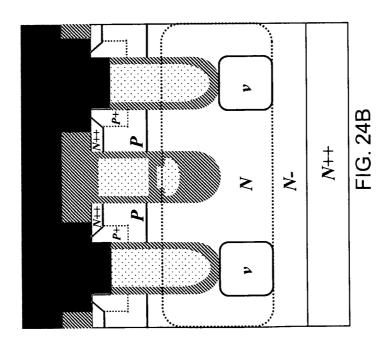

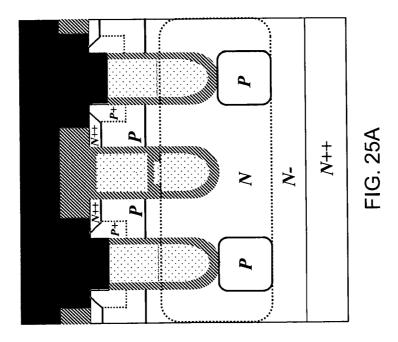

A trench MOSFET contains a recessed field plate (RFP) trench adjacent the gate trench. The RFP trench contains an RFP electrode insulated from the die by a dielectric layer along the walls of the RFP trench. The gate trench has a thick bottom oxide layer, and the gate and RFP trenches are preferably formed in the same processing step and are of substantially the same depth. When the MOSFET operates in the third quadrant (with the source/body-to-drain junction forward-biased), the combined effect of the RFP and gate electrodes significantly reduces in the minority carrier diffusion current and reverse-recovery charge. The RFP electrode also functions as a recessed field plates to reduce the electric field in the channel regions when the MOSFET source/body todrain junction reverse-biased.

#### 27 Claims, 29 Drawing Sheets

U.S. Patent Nov. 30, 2010 Sheet 1 of 29 US 7,843,004 B2

U.S. Patent Nov. 30, 2010 Sheet 2 of 29 US 7,843,004 B2

U.S. Patent Nov. 30, 2010 Sheet 3 of 29 US 7,843,004 B2

U.S. Patent Nov. 30, 2010 Sheet 4 of 29 US 7,843,004 B2

U.S. Patent Nov. 30, 2010 Sheet 5 of 29 US 7,843,004 B2

U.S. Patent Nov. 30, 2010 Sheet 6 of 29 US 7,843,004 B2

U.S. Patent Nov. 30, 2010 Sheet 7 of 29 US 7,843,004 B2

U.S. Patent Nov. 30, 2010 Sheet 8 of 29 US 7,843,004 B2

U.S. Patent Nov. 30, 2010 Sheet 9 of 29 US 7,843,004 B2

U.S. Patent Nov. 30, 2010 Sheet 10 of 29 US 7,843,004 B2

U.S. Patent Nov. 30, 2010 Sheet 11 of 29 US 7,843,004 B2

U.S. Patent Nov. 30, 2010 Sheet 12 of 29 US 7,843,004 B2

U.S. Patent Nov. 30, 2010 Sheet 13 of 29 US 7,843,004 B2

U.S. Patent Nov. 30, 2010 Sheet 14 of 29 US 7,843,004 B2

U.S. Patent Nov. 30, 2010 Sheet 15 of 29 US 7,843,004 B2

U.S. Patent Nov. 30, 2010 Sheet 16 of 29 US 7,843,004 B2

U.S. Patent Nov. 30, 2010 Sheet 17 of 29 US 7,843,004 B2

U.S. Patent Nov. 30, 2010 Sheet 18 of 29 US 7,843,004 B2

U.S. Patent Nov. 30, 2010 Sheet 19 of 29 US 7,843,004 B2

U.S. Patent Nov. 30, 2010 Sheet 20 of 29 US 7,843,004 B2

Appx23

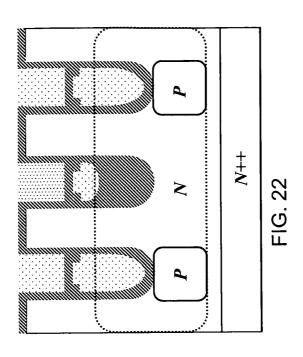

U.S. Patent Nov. 30, 2010 Sheet 21 of 29 US 7,843,004 B2

Appx24

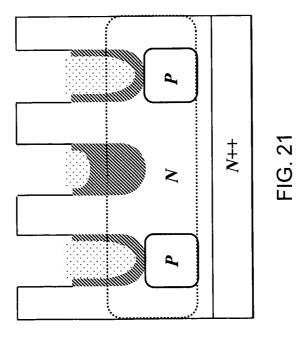

U.S. Patent Nov. 30, 2010 Sheet 22 of 29 US 7,843,004 B2

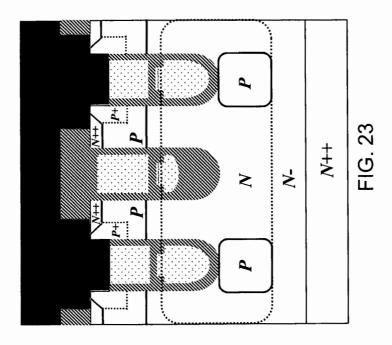

U.S. Patent Nov. 30, 2010 Sheet 23 of 29 US 7,843,004 B2

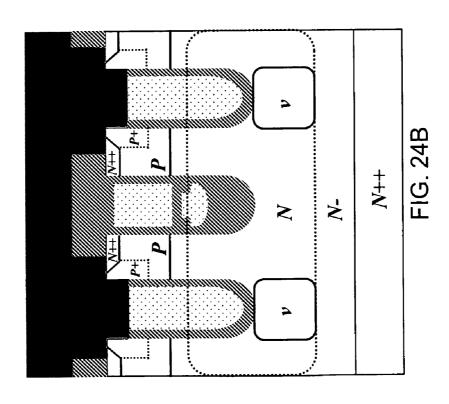

U.S. Patent Nov. 30, 2010 Sheet 24 of 29 US 7,843,004 B2

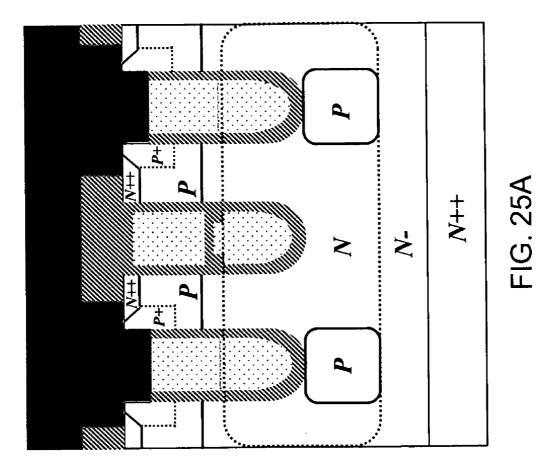

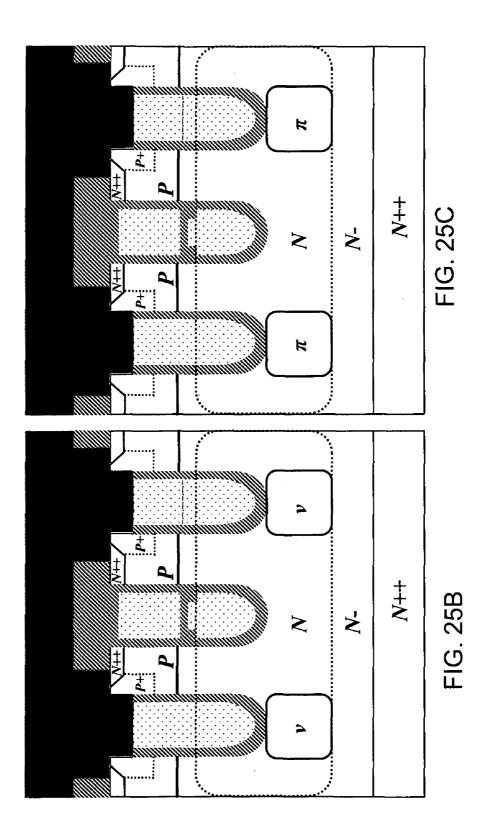

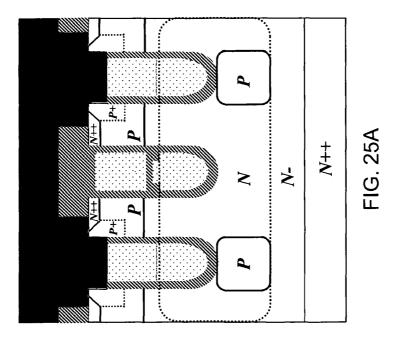

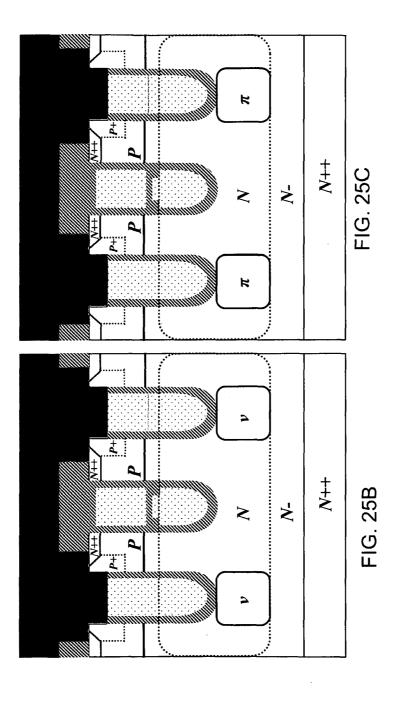

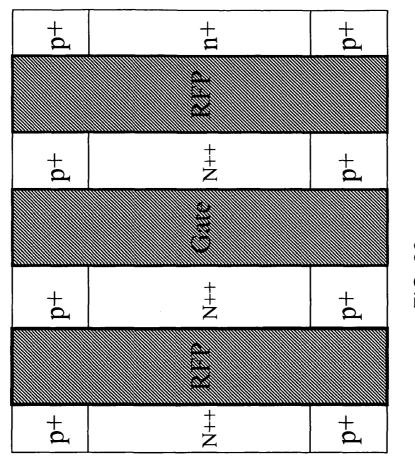

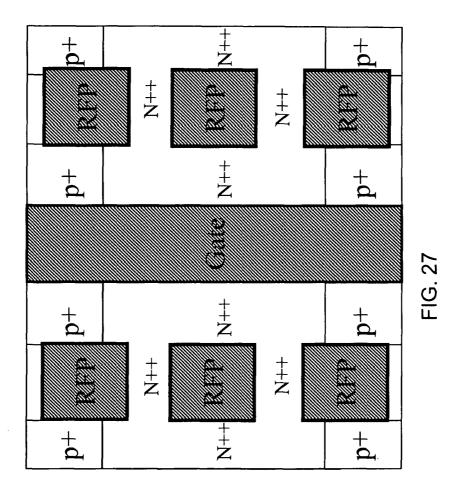

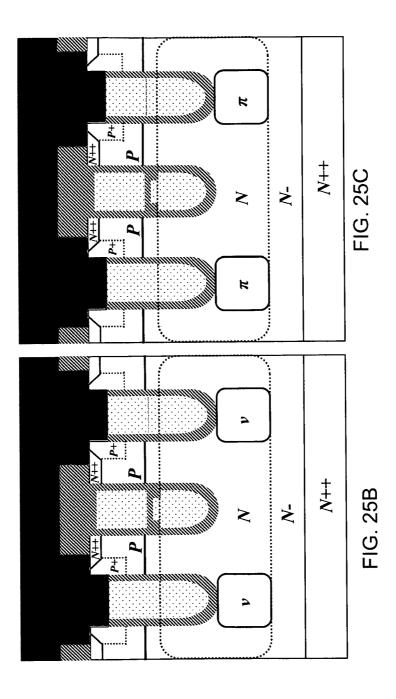

U.S. Patent Nov. 30, 2010 Sheet 25 of 29 US 7,843,004 B2

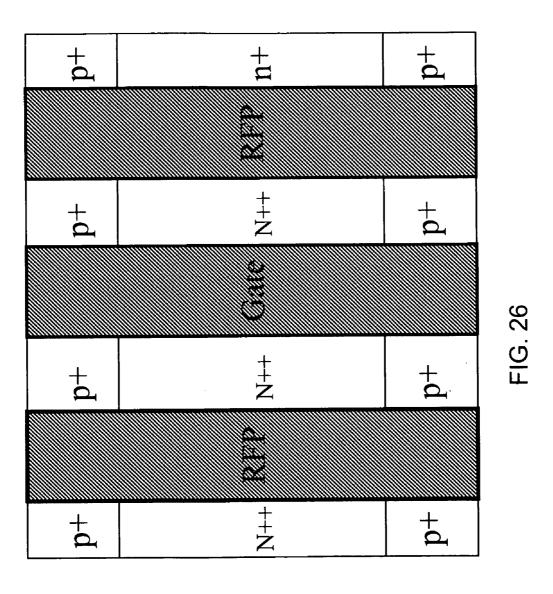

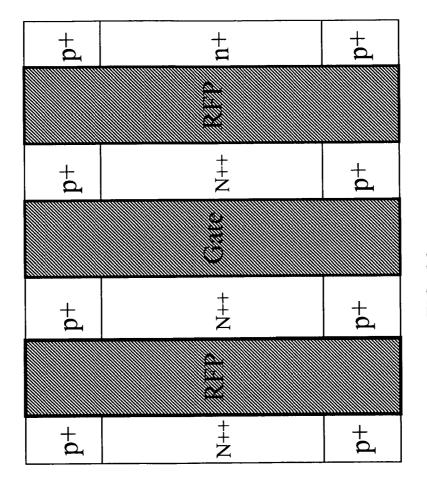

U.S. Patent Nov. 30, 2010 Sheet 26 of 29 US 7,843,004 B2

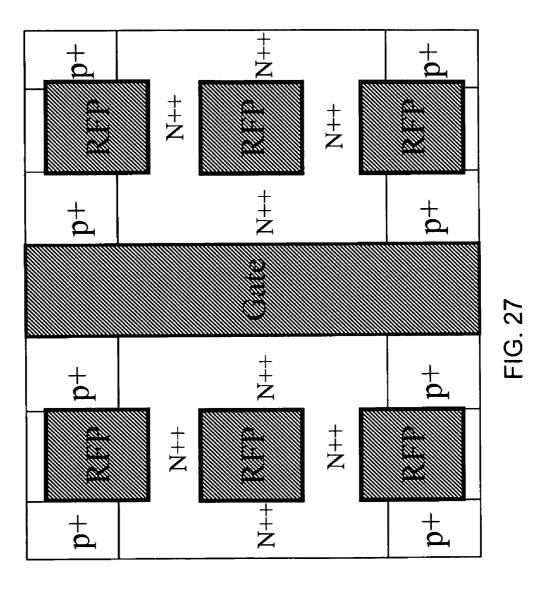

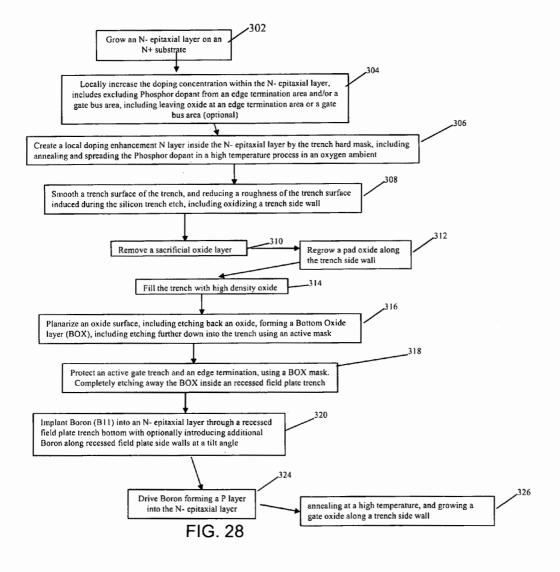

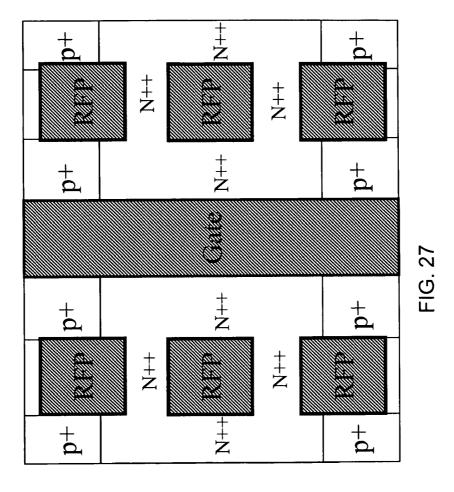

U.S. Patent Nov. 30, 2010 Sheet 27 of 29 US 7,843,004 B2

U.S. Patent Nov. 30, 2010 Sheet 28 of 29 US 7,843,004 B2

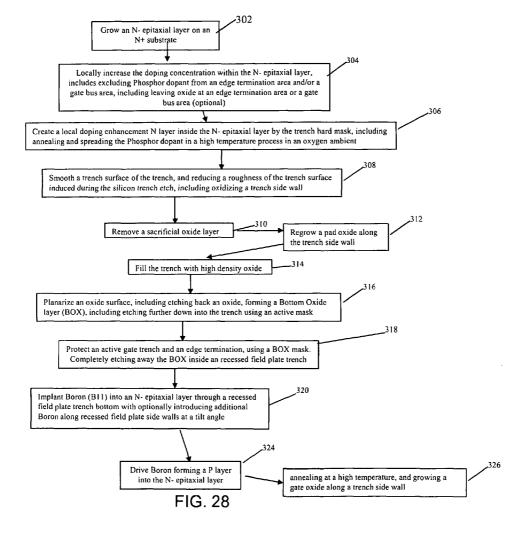

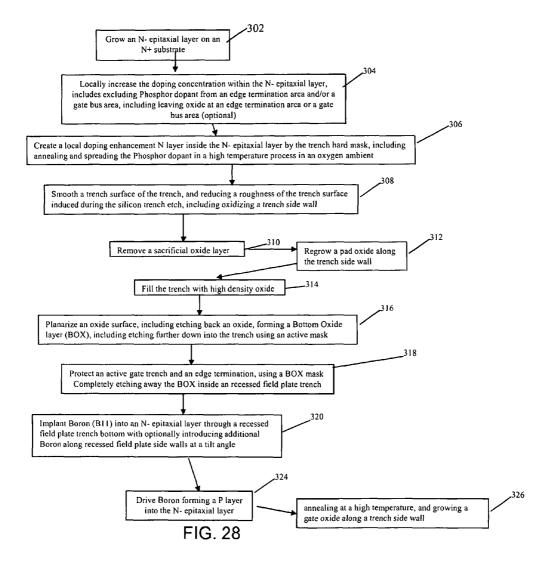

U.S. Patent

Nov. 30, 2010

**Sheet 29 of 29**

US 7,843,004 B2

Case: 21-1709 Document: 10 Page: 66 Filed: 05/03/2021

### US 7,843,004 B2

## POWER MOSFET WITH RECESSED FIELD PLATE

## CROSS-REFERENCE TO RELATED APPLICATIONS

This application claims the priority of Provisional Application No. 60/847,551, filed Sep. 27, 2006, which is incorporated herein by reference in its entirety.

### BACKGROUND OF THE INVENTION

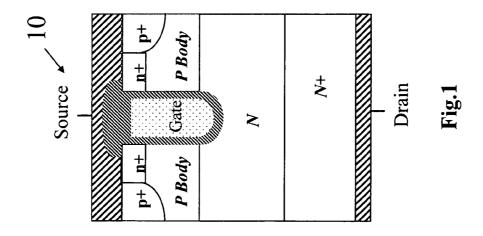

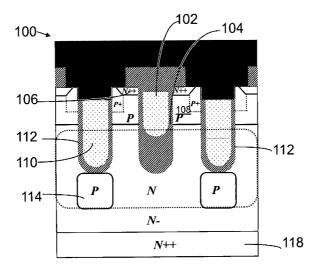

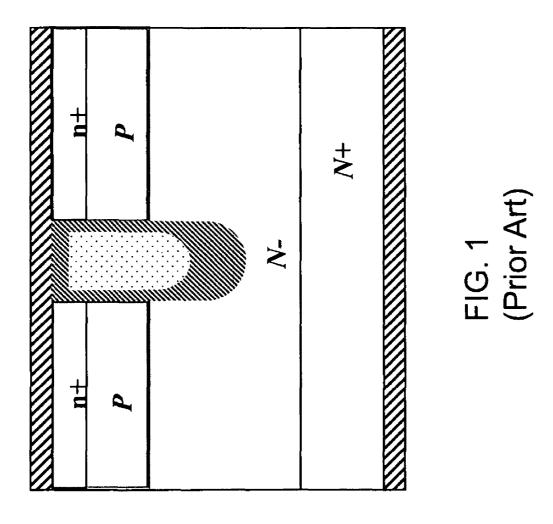

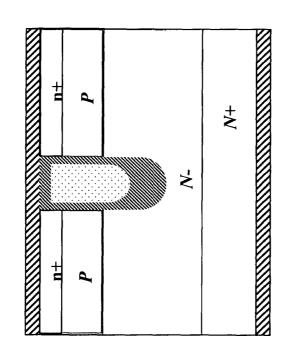

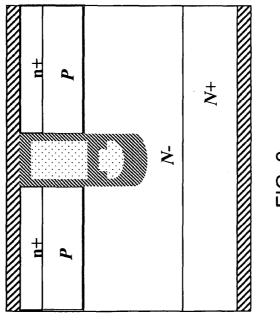

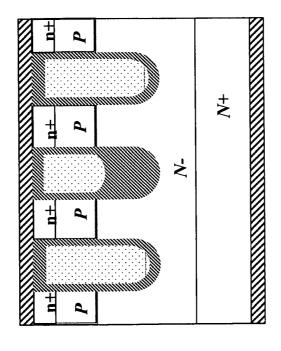

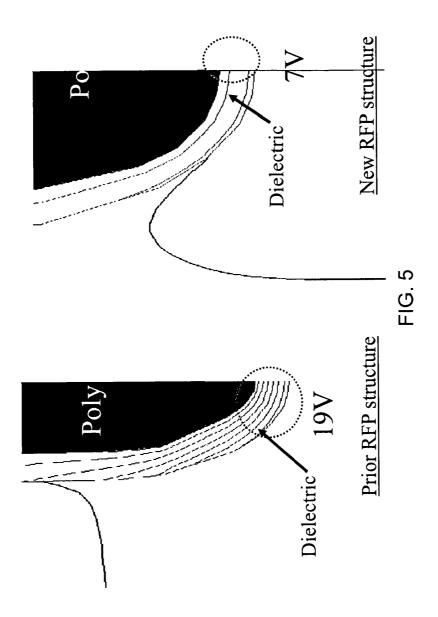

Power MOSFETs are widely used as switching devices in many electronic applications. In order to minimize conduction power loss it is desirable that power MOSFETs have a 15 low specific on-resistance, which is defined as the product of the on-resistance (Ron) of the MOSFET multiplied by the active die area (A) of the MOSFET (Ron\*A). A trench-type MOSFET, as shown in the schematic cross-sectional view of a MOSFET 10 in FIG. 1, provides a low specific on-resistance 20 because of its high packing density or number of cells per unit area. As the cell density increases, the associated capacitances, such as the gate-to-source capacitance (Cgs), the gateto-drain capacitance (Cgd), and the drain-to-source capacitance (Cds), also increase. In many switching applications 25 such as the synchronous buck dc-dc converters used in mobile products, MOSFETs with a breakdown voltage in the range of 12 to 30V are required to operate at switching frequencies approaching 1 MHz. Therefore, it is desirable to minimize the switching or dynamic power loss caused by these capacitances. The magnitudes of these capacitances are directly proportional to the gate charge (Qg), the gate-drain charge (Qgd), and output charge (Qoss). Furthermore, when these devices operate in the third quadrant, i.e. where the drainbody junction is forward-biased, charge is stored as a result of 35 minority carrier injection, and this stored charge causes a delay in switching speed of the device. It is therefore critical that a MOSFET switch have a low reverse recovery charge

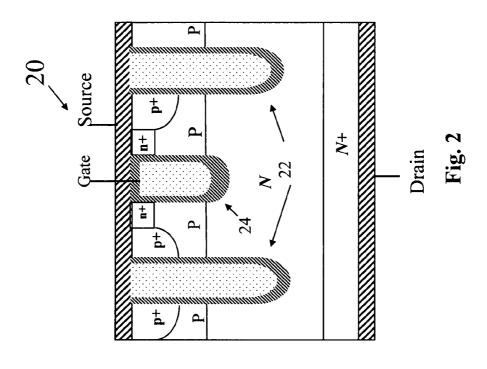

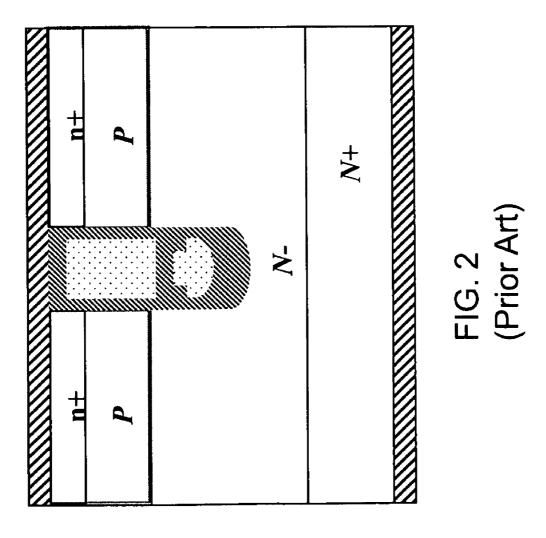

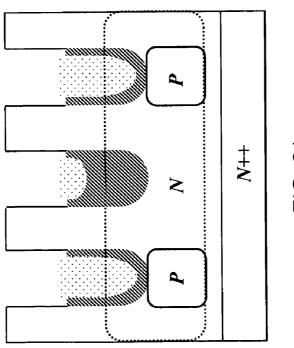

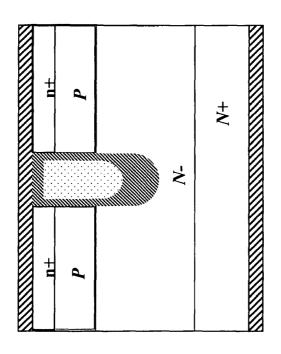

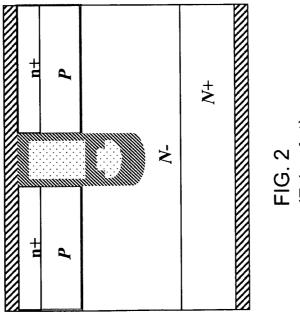

U.S. Pat. No. 6,710,403 to Sapp proposes a dual-trench 40 power MOSFET, as shown in FIG. 2, with two deeper polysilicon-filled trenches 22 on either side of an active trench 24, to lower the levels of Ron, Cgs and Cgd. However, MOSFET 20 does not lower the reverse recovery charge Qrr and requires the fabrication of trenches having two different 45 depths. Furthermore, in MOSFET 20 the deep and shallow trenches are not self-aligned, which causes variations in mesa widths and hence in breakdown voltages.

As the switching-speed requirements increase to 1 MHz and above, driven by new applications such as CPU voltage regulator module (VRM), power MOSFETs are becoming increasingly unable to operate with satisfactory efficiency performance and power loss. Therefore, there is a clear need for a power MOS transistor that has low gate charges Qg and Qgd, a low output charge Qoss and a low reverse-recovery charge Qrr, in addition to having a low specific on-resistance (Ron\*A).

### BRIEF SUMMARY OF THE INVENTION

A MOSFET according to the invention is formed in a semiconductor die and comprises a gate trench and a recessed field plate (RFP) trench that are self-aligned, both trenches extending from a surface of the die and forming a mesa between them. The gate trench comprises a gate electrode 65 separated from the die by a first dielectric layer having a thick section at the bottom of the gate trench and extends to sub-

2

stantially the same depth as the RFP trench. The RFP trench contains an RFP electrode separated from the die by a second dielectric layer. The MOSFET also comprises a source region of a first conductivity type adjacent the surface of the die and a sidewall of the gate trench and adjacent to the RFP electrode trench in some areas of the MOSFET and a body region of a second conductivity type opposite to the first conductivity type adjacent the sidewall of the gate trench and the source region. In some areas of the MOSFET, a p+ body contact region may be placed laterally adjacent to the P- body. The RFP electrode may be independently biased or may be biased at the source potential In one embodiment, the respective depths of the gate and RFP trenches are substantially the same.

The invention also comprises a method of fabricating a MOSFET. The method comprises providing a semiconductor die; etching the die so as to form a gate trench and a recessed field plate (RFP) trench, the gate trench and the RFP trench extending from a surface of the die and being of substantially equal depth; forming an insulating layer at a bottom of the gate trench; forming a gate dielectric layer on a sidewall of the gate trench above the insulating layer; forming a second dielectric layer along the walls of the RFP trench; introducing conductive material into the gate trench to form a gate electrode; introducing conductive material into the RFP trench to form an RFP electrode; implanting dopant of a second conductivity type opposite to the first conductivity type to form a body region in the mesa adjacent the sidewall of the gate trench; implanting dopant of a first conductivity type to form a source region adjacent the surface of the die in the mesa; and depositing a source contact layer on the surface of the die in contact with the source region.

### BRIEF DESCRIPTION OF THE SEVERAL VIEWS OF THE DRAWING

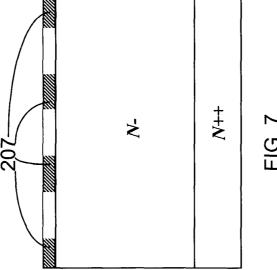

${\rm FIG.}~1$  is a cross-sectional view of a conventional trenchtype MOSFET.

FIG. 2 is a cross-sectional view of a known dual-trench MOSFET.

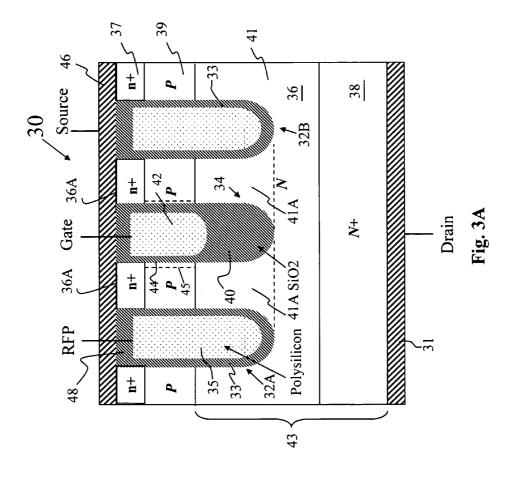

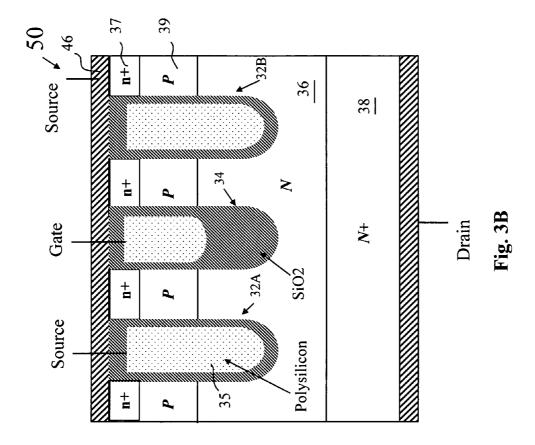

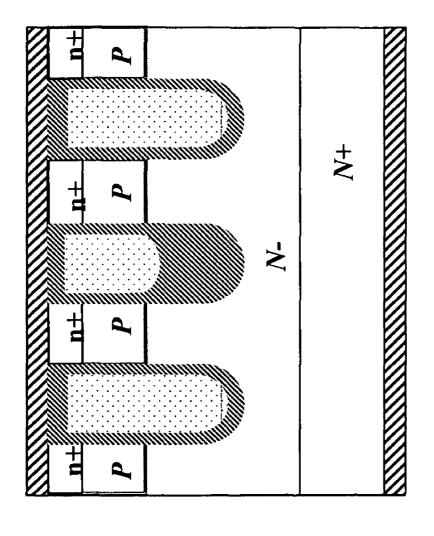

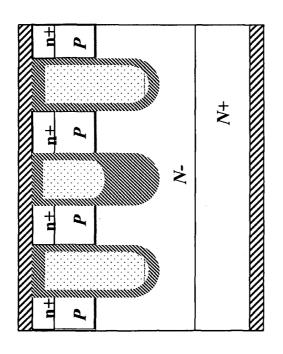

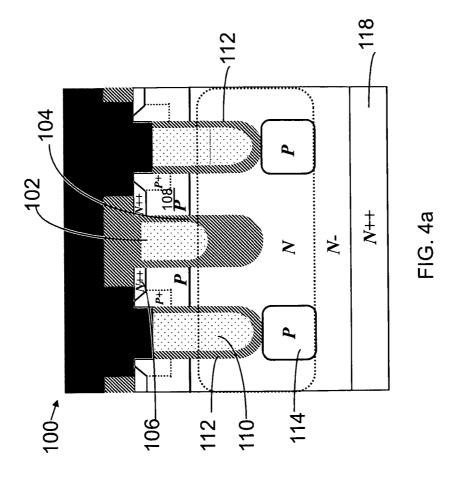

FIG. 3A is a cross-sectional view of a MOSFET having a recessed field plate (RFP) in accordance with the invention, with the recessed field plate (RFP) electrode independently biased.

FIG. 3B is a cross-sectional view of a MOSFET having a recessed field plate (RFP) in accordance with the invention, with the RFP electrode biased at the same potential as the source.

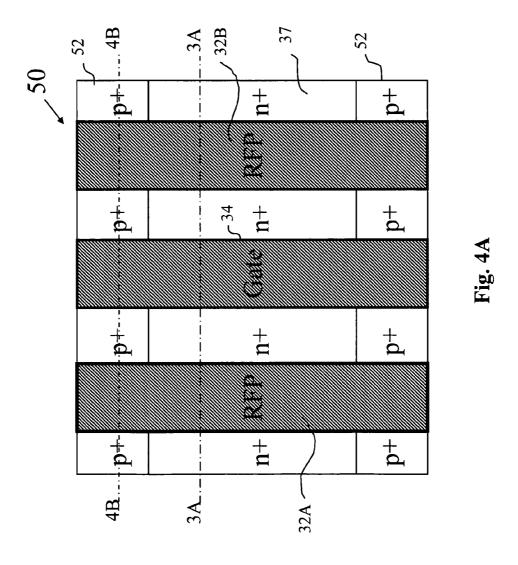

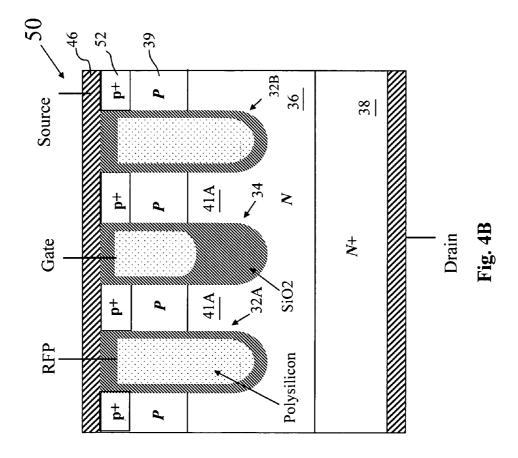

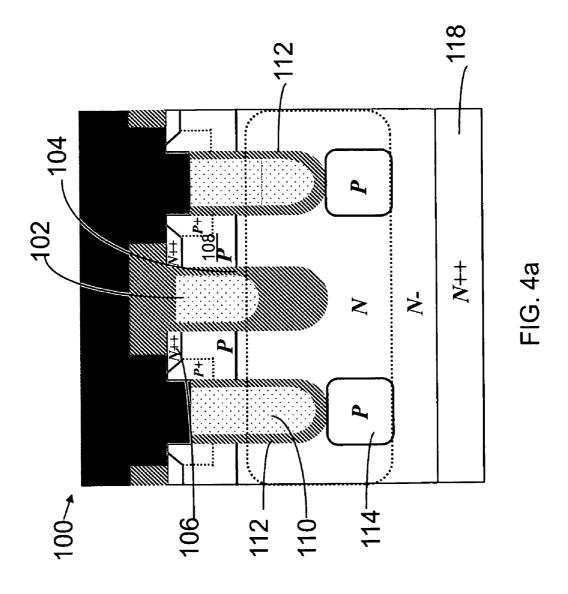

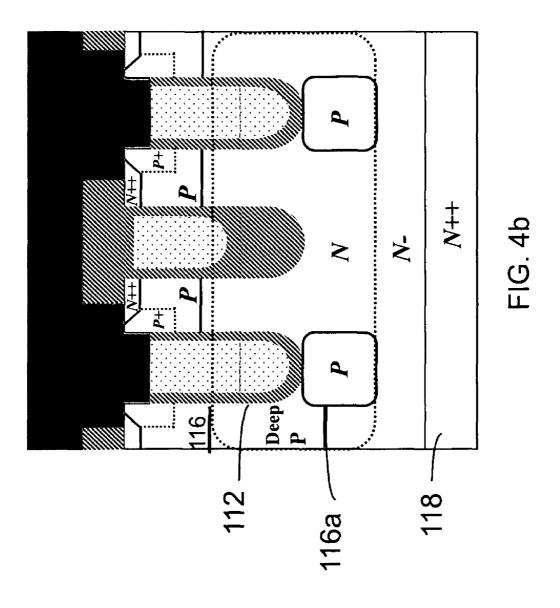

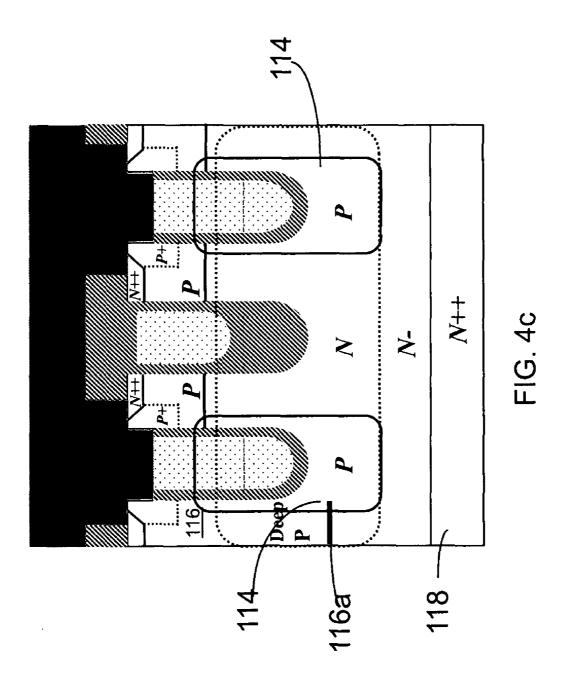

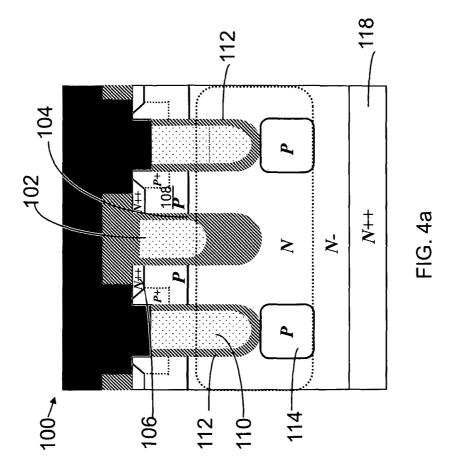

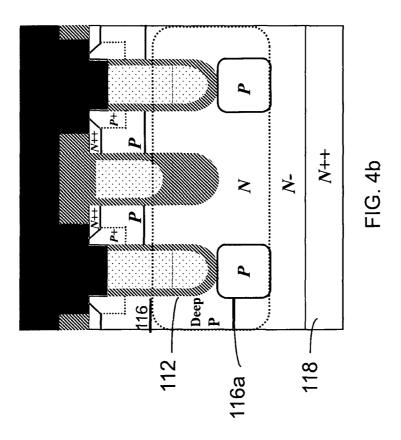

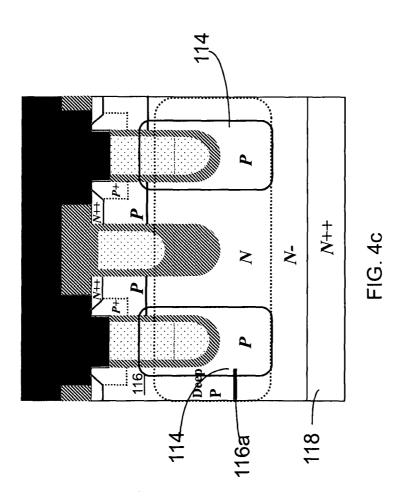

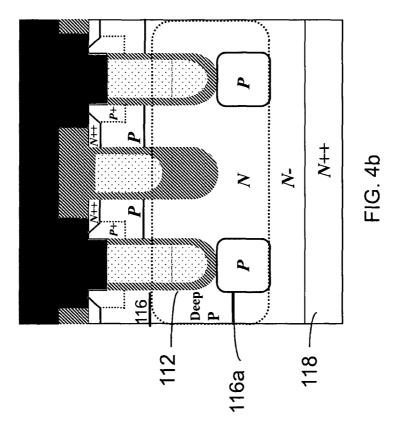

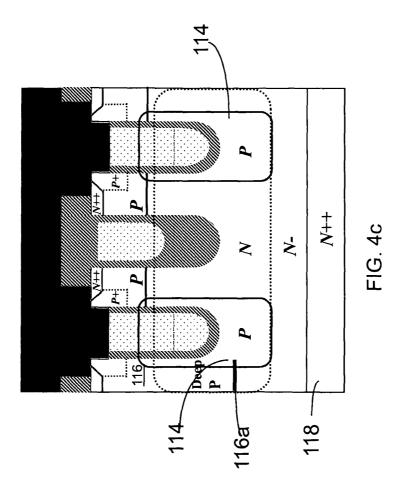

FIG. 4A is a top view of the MOSFET shown in FIG. 3A. FIG. 4B is a cross-sectional view of the MOSFET shown in FIG. 3A, taken at cross-section 4B-4B in FIG. 4A.

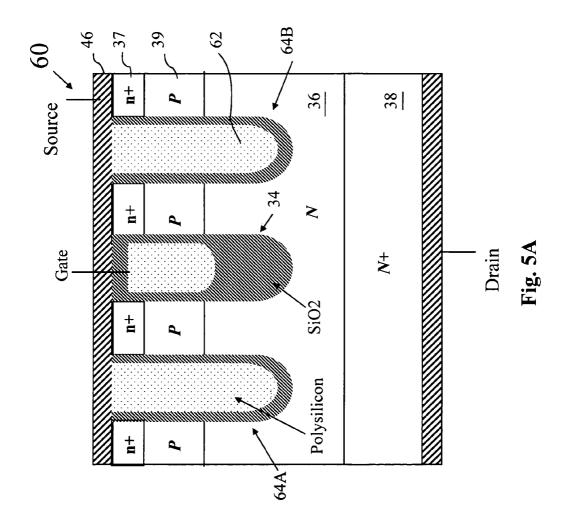

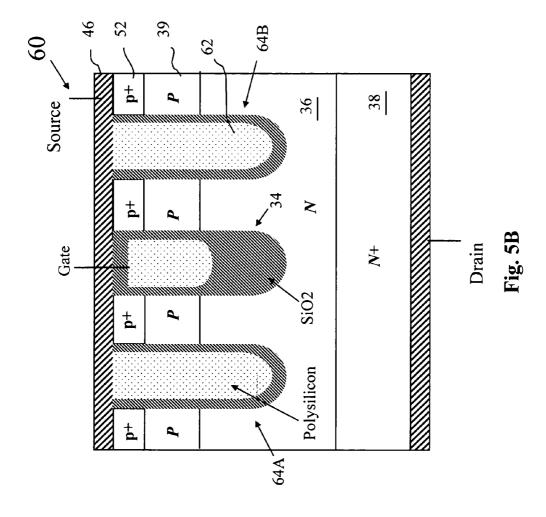

FIG. **5**A is a cross-sectional view of an alternative embodiment wherein the RFP electrode is in contact with the source region.

FIG. 5B is a cross-sectional view of the MOSFET of FIG. 5A taken at a cross-section corresponding to cross-section 4B-4B in FIG. 4A.

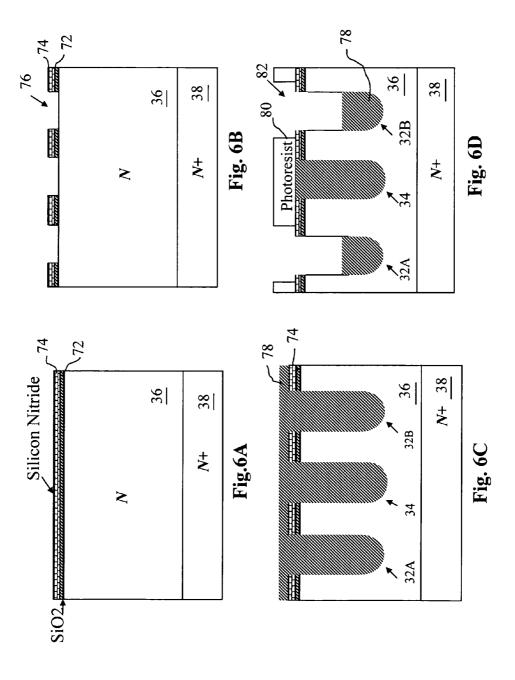

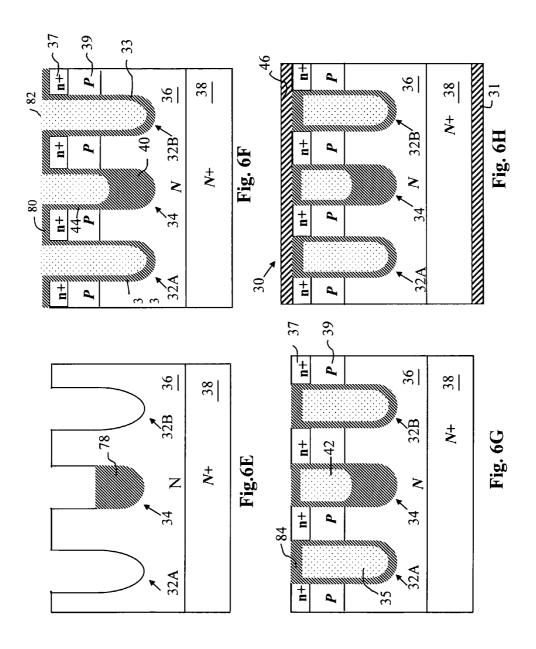

FIGS. 6A-6H illustrate a process of fabricating the MOS-FET shown in FIG. 3A.

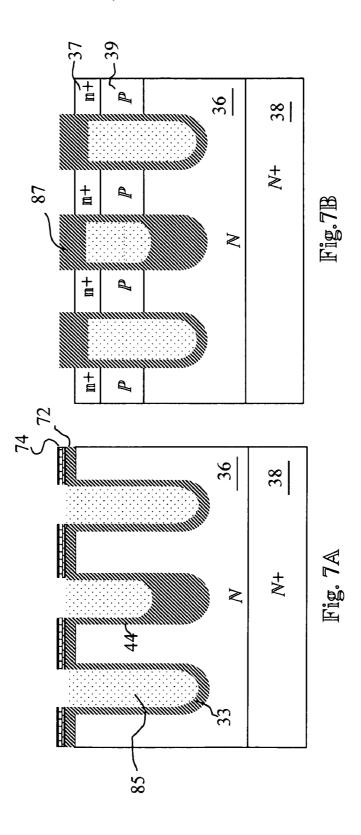

FIGS. 7A and B illustrate an alternative version of a portion of the process shown in FIGS. 6A-6H.

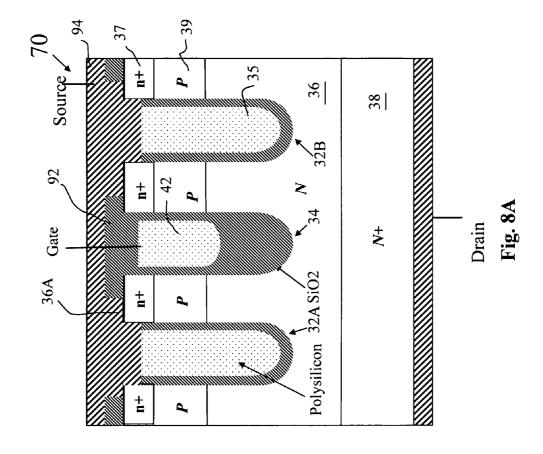

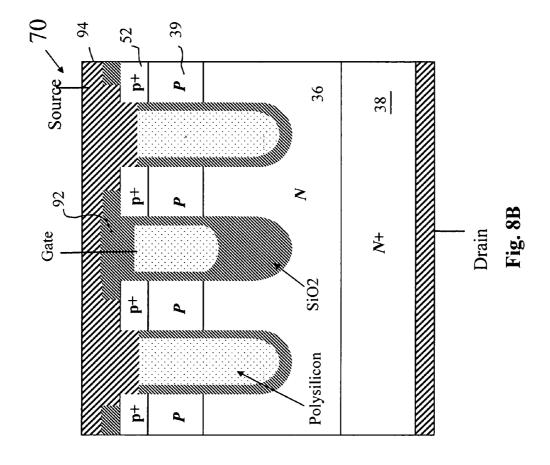

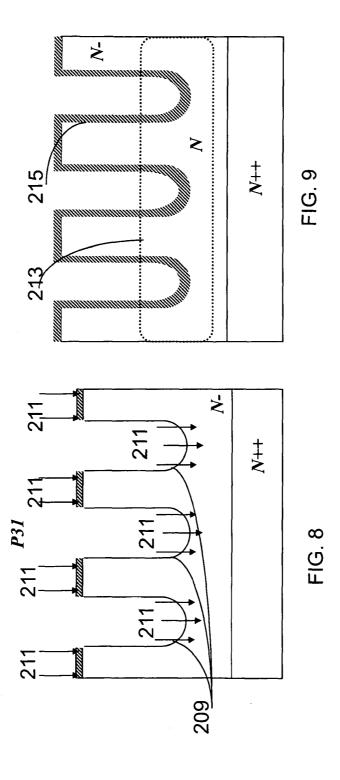

FIGS. **8**A and **8**B are cross-sectional views of a MOSFET according to the invention wherein an insulating layer above the gate trench overlaps a portion of the source regions and the source contact layer contacts the RFP electrodes.

### US 7,843,004 B2

3

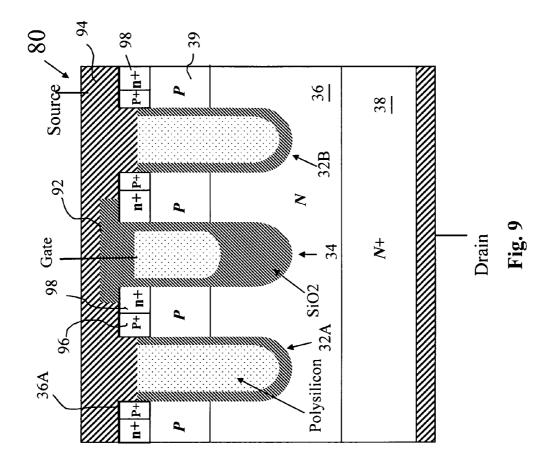

FIG. 9 is a cross-sectional view of a MOSFET similar to the MOSFET of FIGS. 8A and 8B wherein body contact regions are formed laterally adjacent to the source regions.

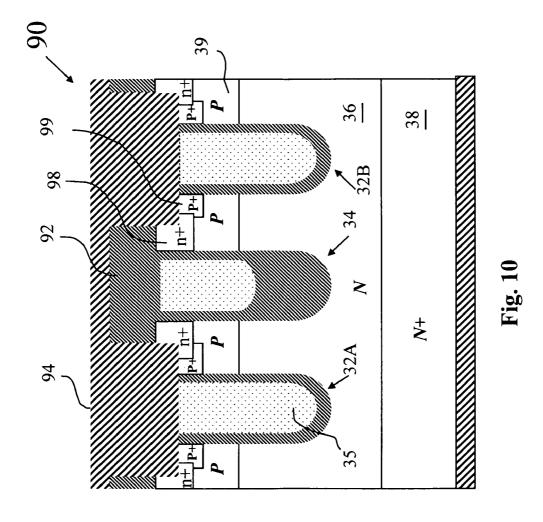

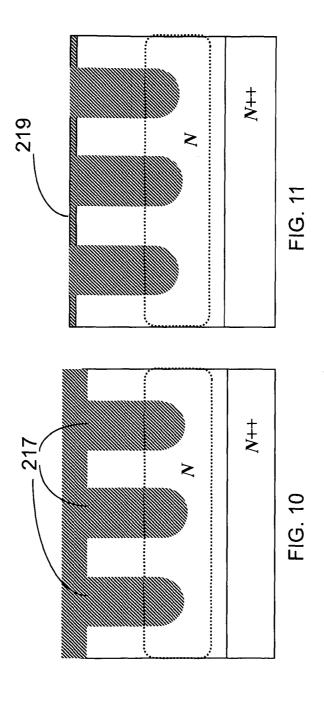

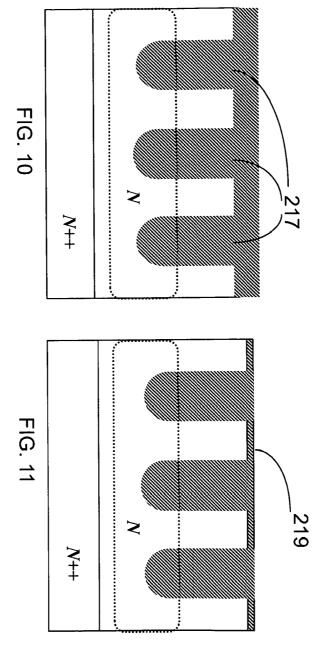

FIG. 10 is a cross-sectional view of an MOSFET similar to the MOSFET of FIG. 9 wherein the body contact regions 5 extend to a level below the source regions.

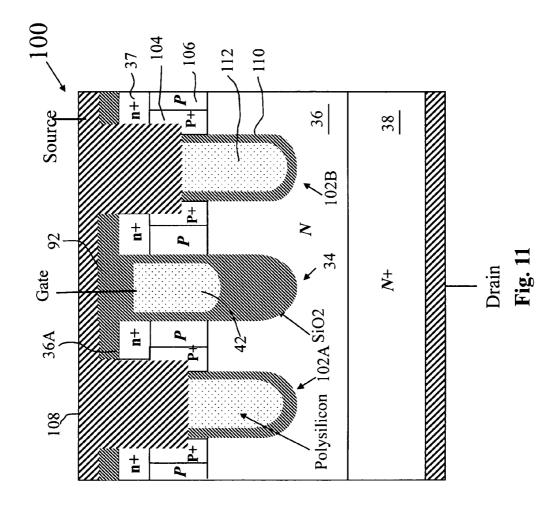

FIG. 11 is a cross-sectional view of a MOSFET according to the invention wherein the RFP electrodes are recessed and body contact regions are formed laterally adjacent to the body regions.

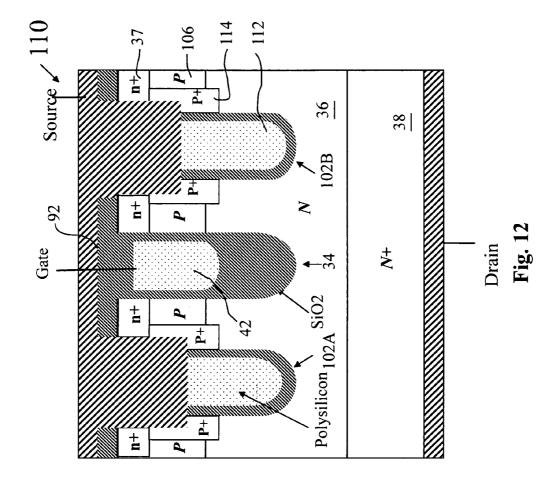

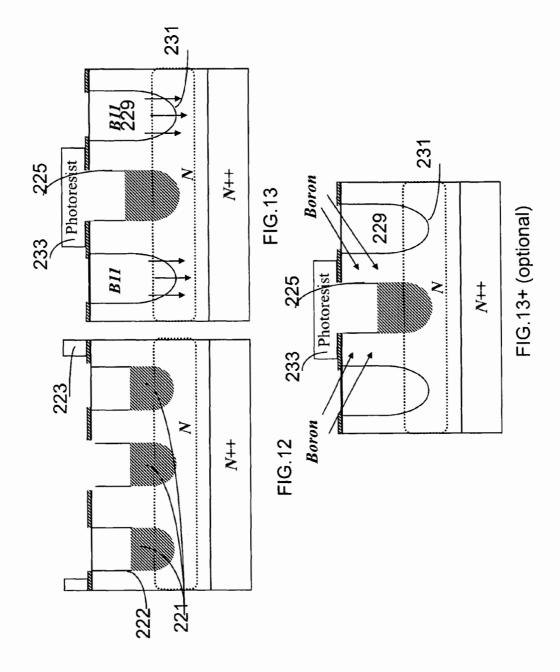

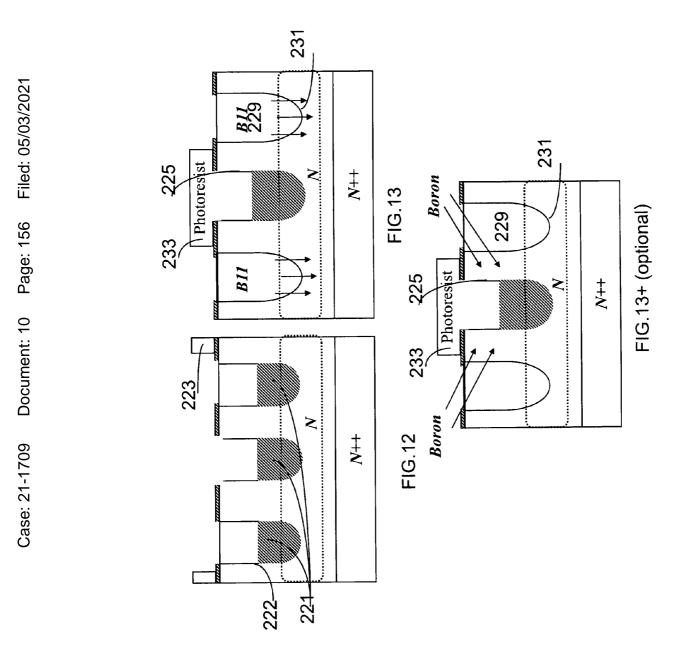

FIG. 12 is a cross-sectional view of a MOSFET similar to the MOSFET of FIG. 11 wherein the body contact regions extend to a level below the body regions.

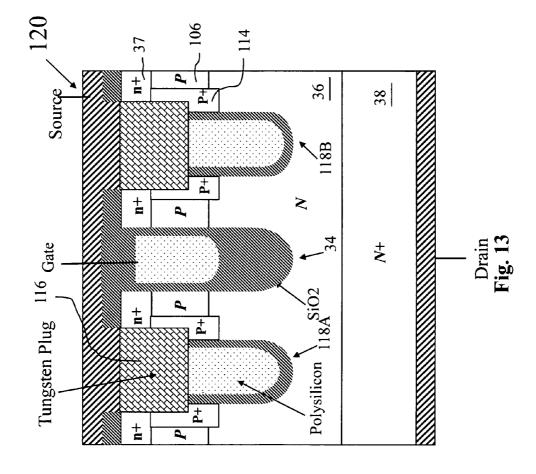

FIG. 13 is a cross-sectional view of a MOSFET similar to the MOSFET of FIG. 12 wherein metal plugs are formed in 1 the upper portions of the RFP trenches.

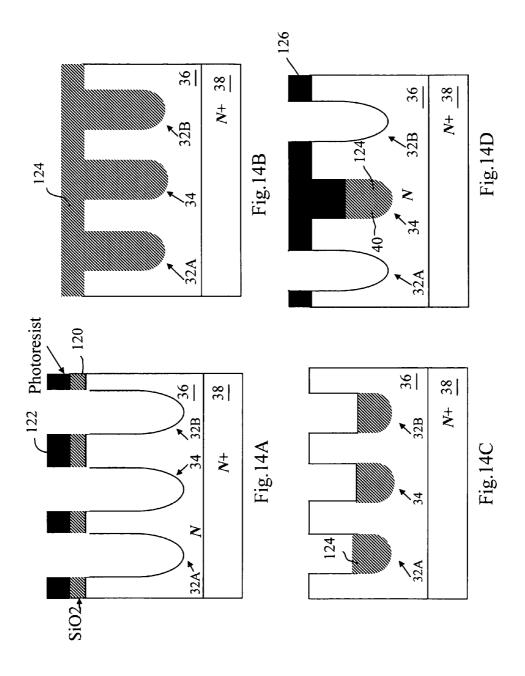

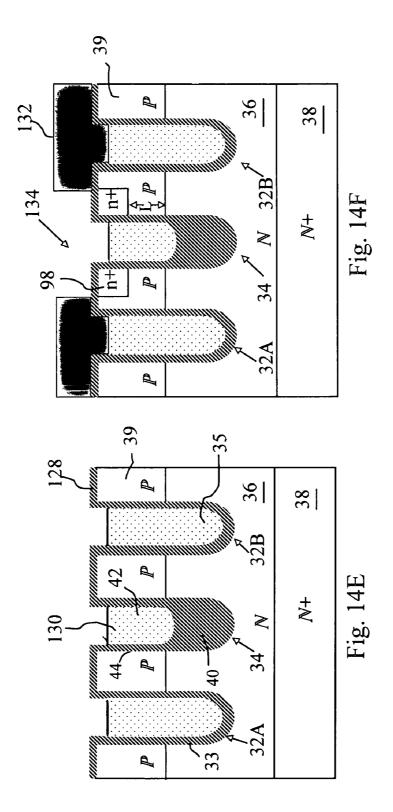

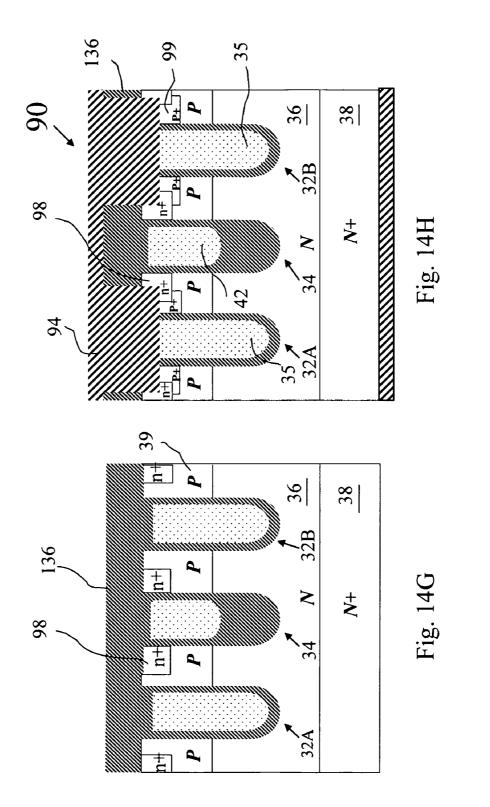

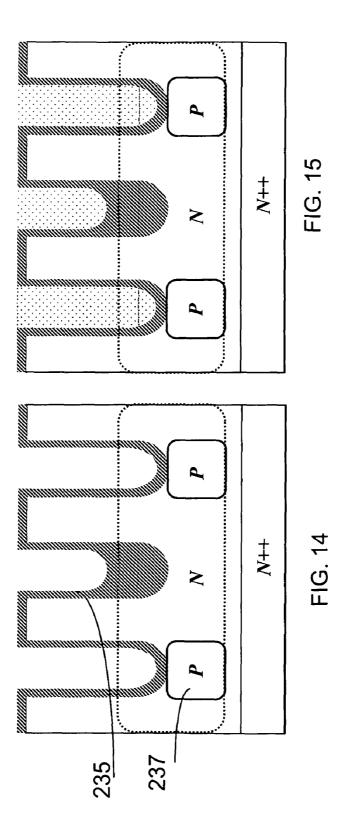

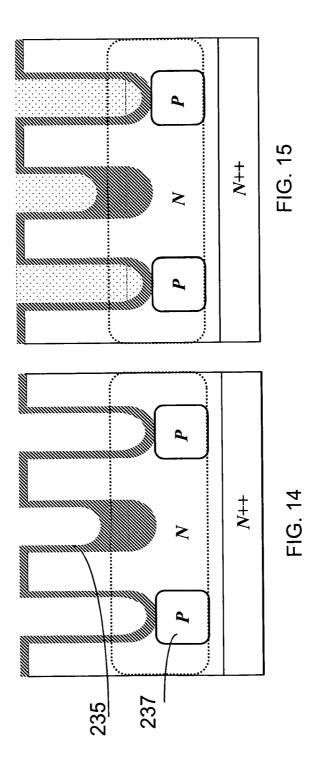

FIGS. 14A-14H illustrate a process of fabricating the MOSFET shown in FIG. 10.

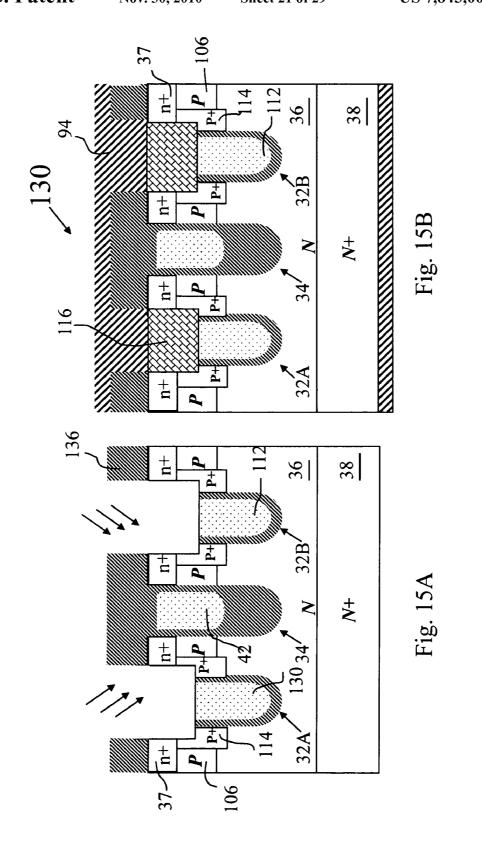

FIGS. 15A and 15B illustrate a variation of the process shown in FIGS. 14A-14H.

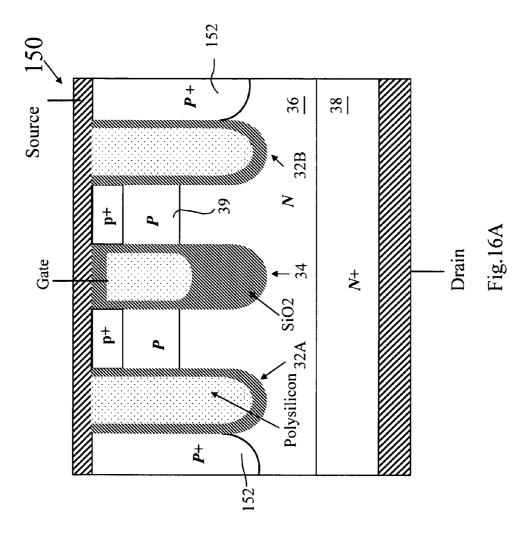

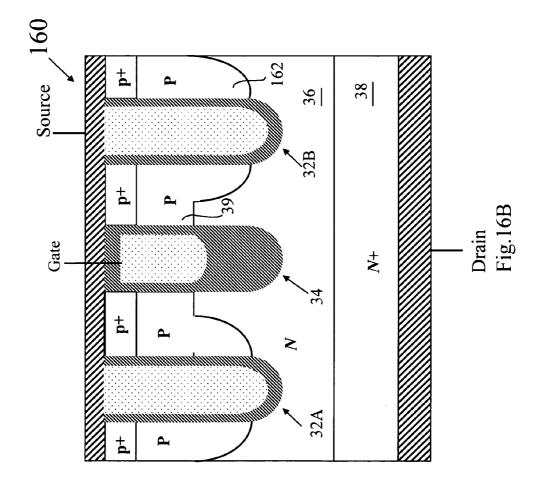

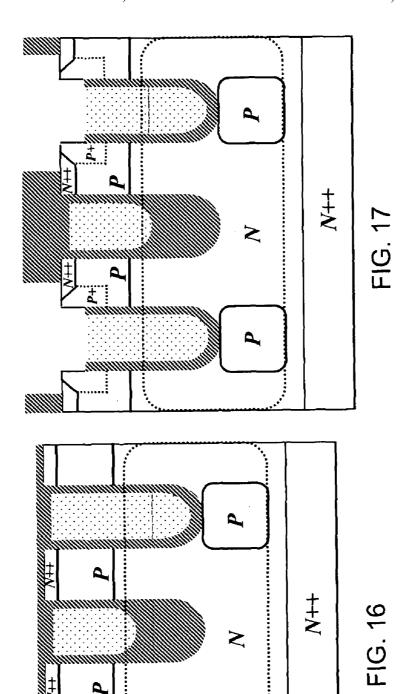

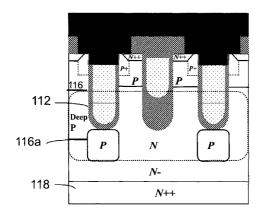

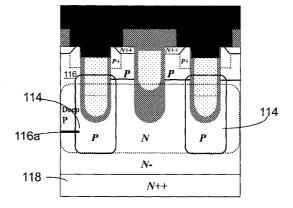

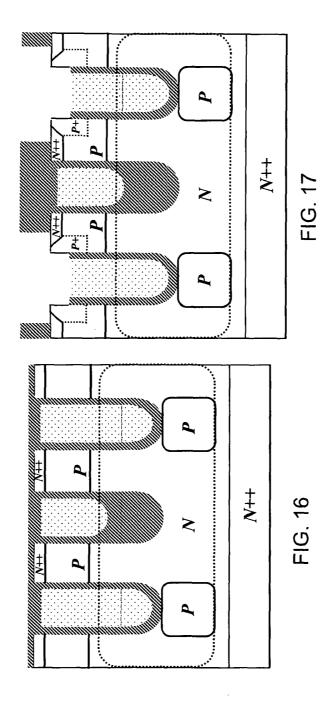

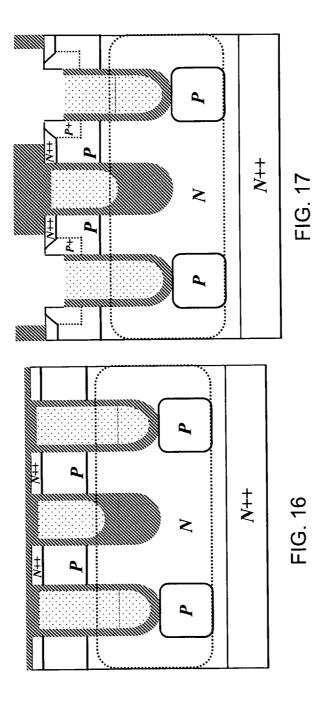

FIGS. **16**A and **16**B are cross-sectional views of MOS-FETs according to the invention that contain deep p-type regions to limit the breakdown voltage of the MOSFET.

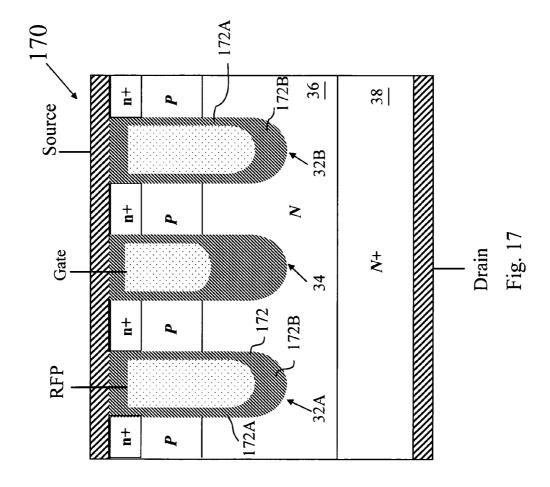

FIG. 17 is a cross-sectional view of a MOSFETs according to the invention wherein the RFP trenches contain a thick 25 bottom oxide layer.

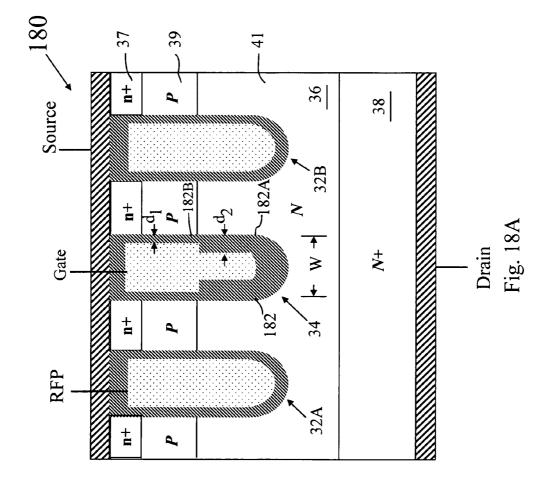

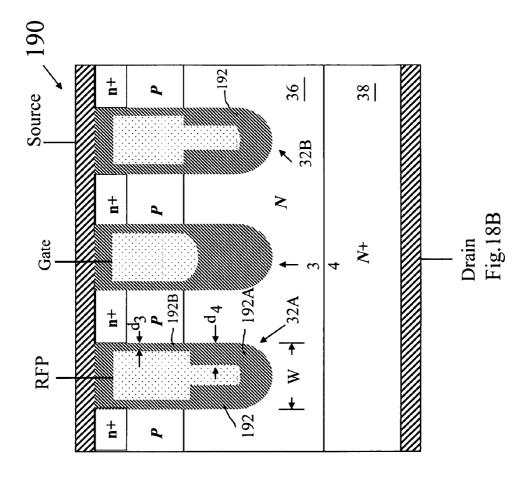

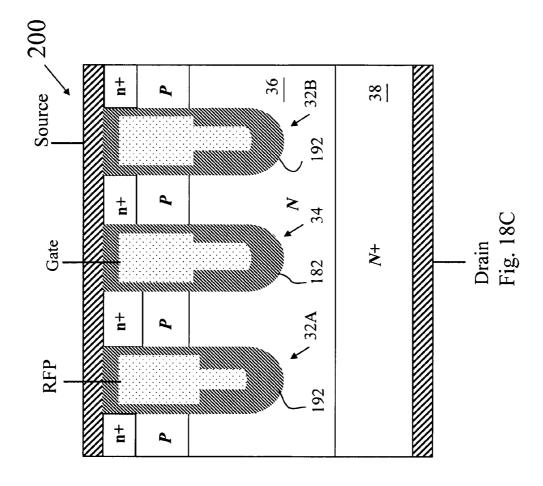

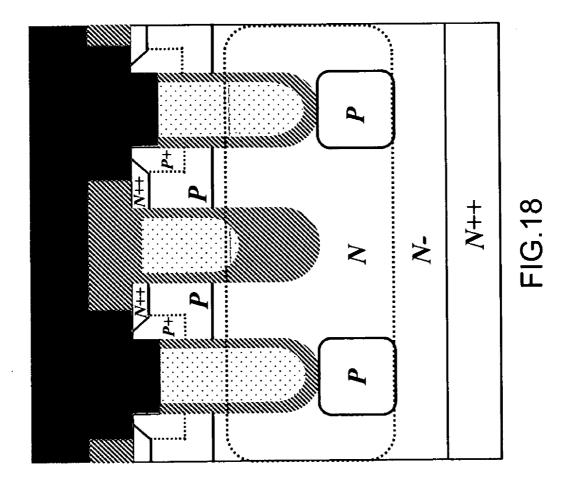

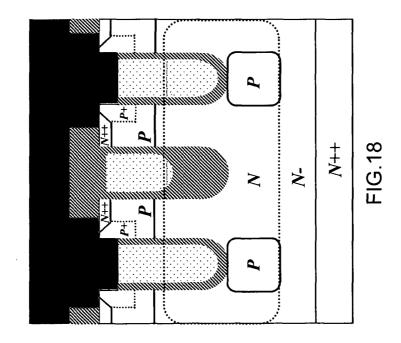

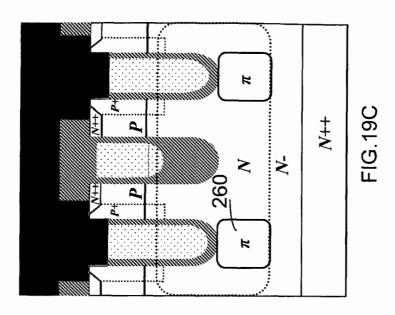

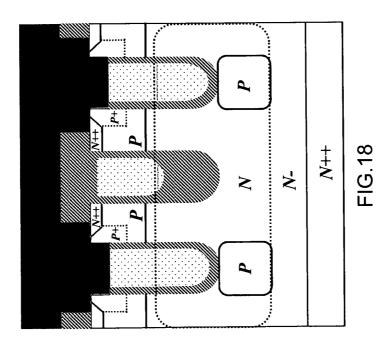

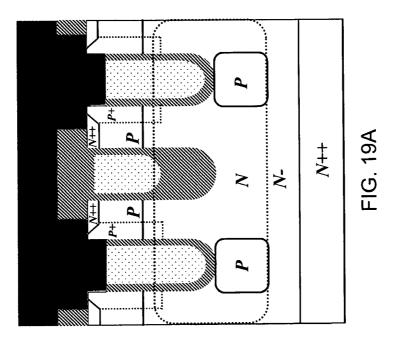

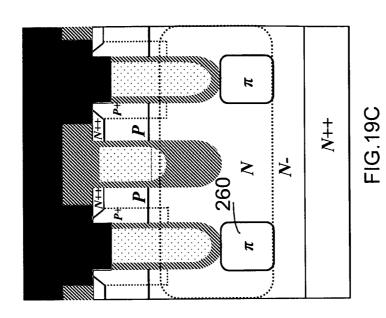

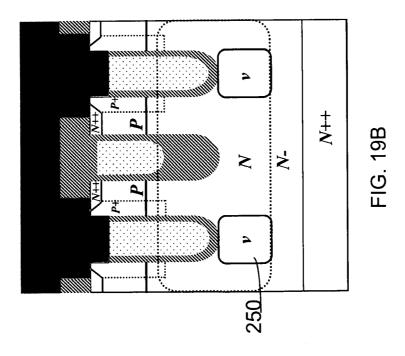

FIGS. 18A-18C are cross-sectional views of MOSFETs containing a stepped oxide layer in the gate trench and/or the RFP trenches.

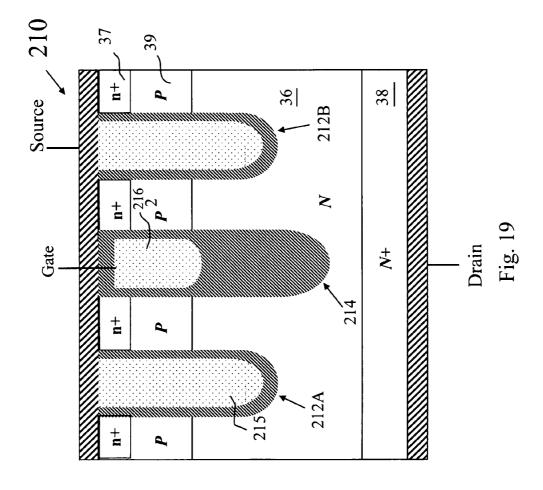

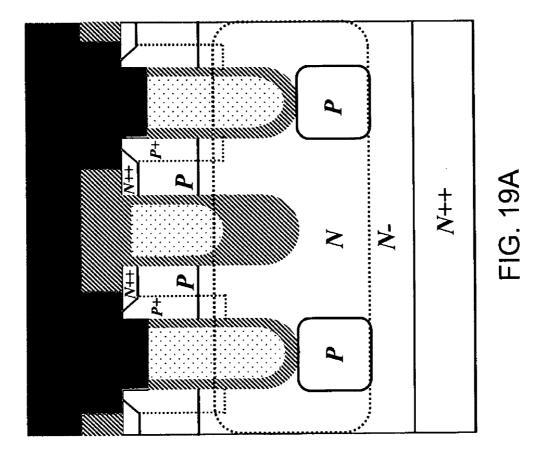

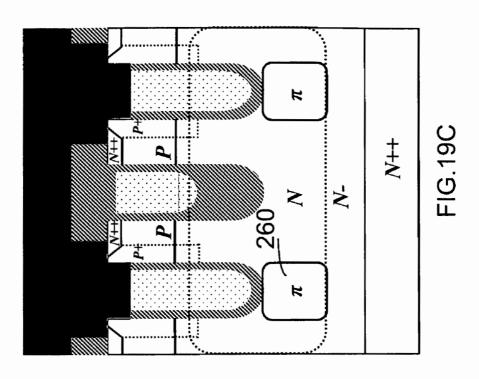

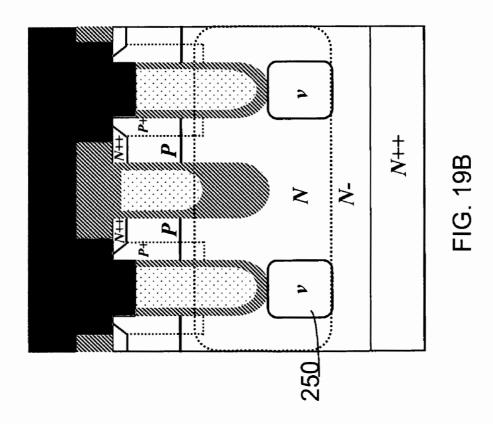

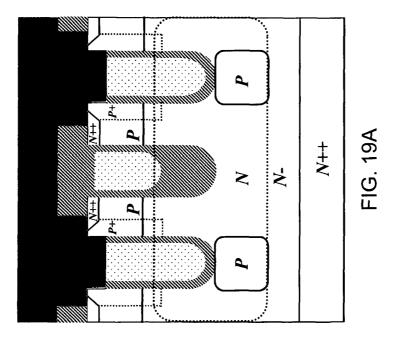

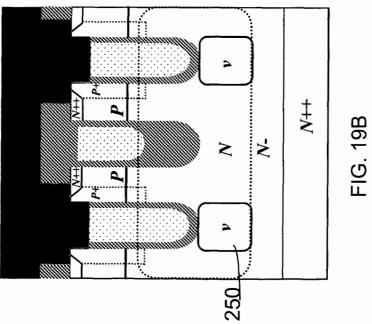

FIG. **19** is a cross-sectional view of a MOSFET wherein the 30 gate trench is deeper than the RFP trenches.

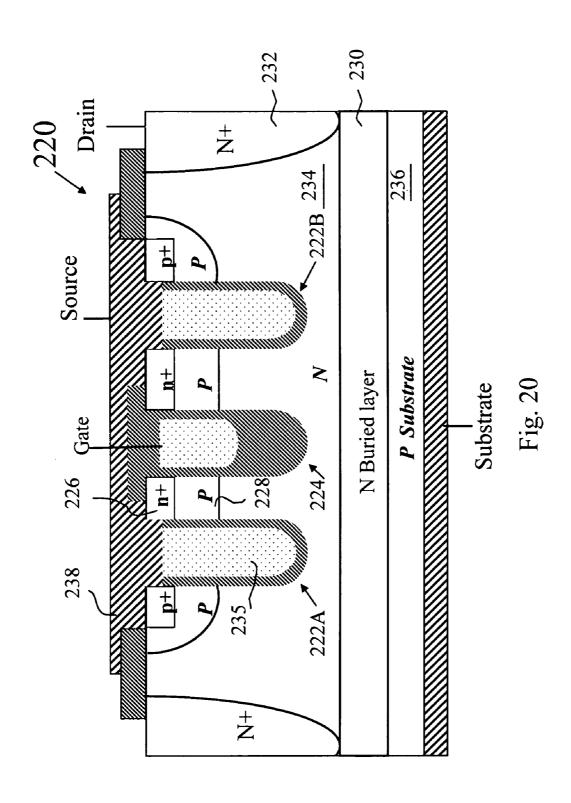

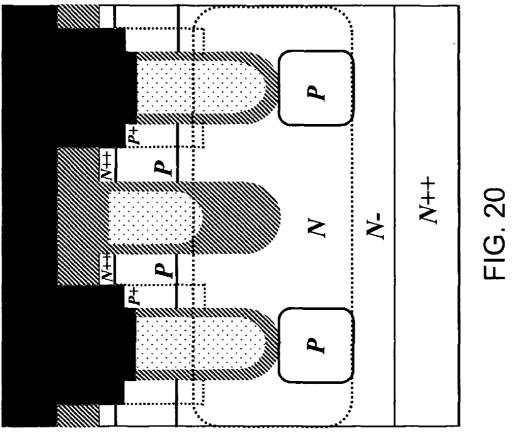

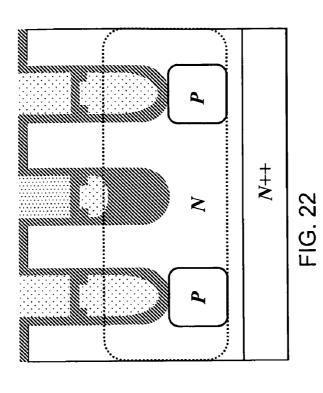

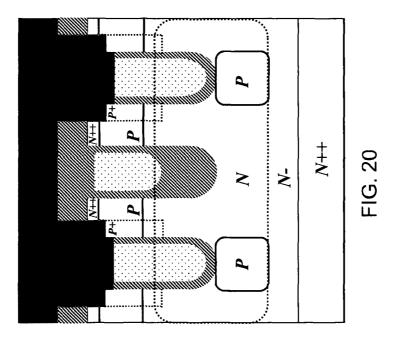

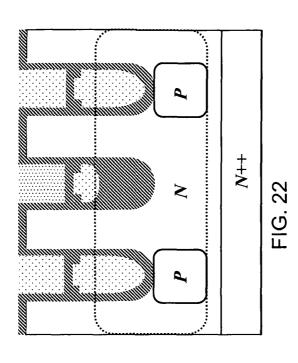

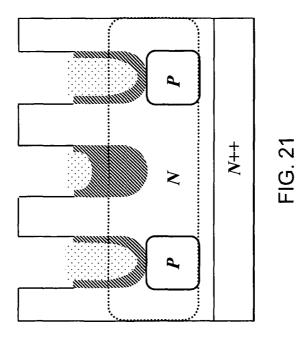

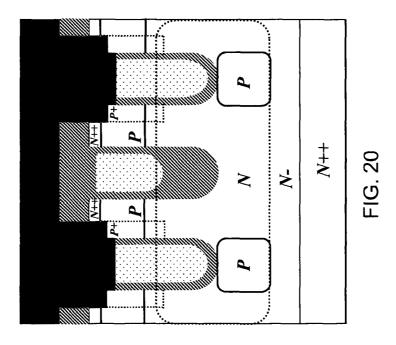

FIG. 20 is a cross-sectional view of a quasi-vertical MOS-FET in accordance with the invention.

### DETAILED DESCRIPTION OF THE INVENTION

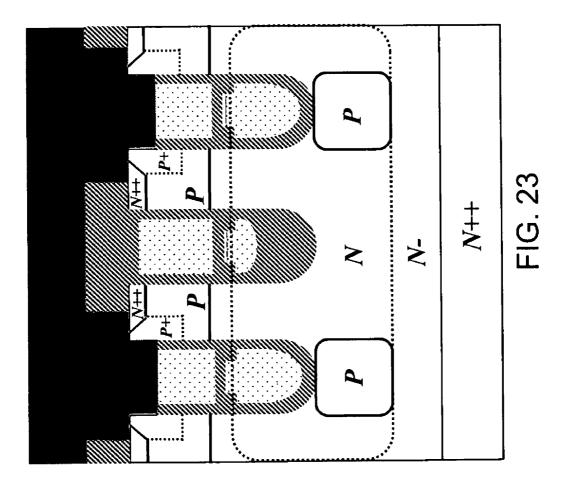

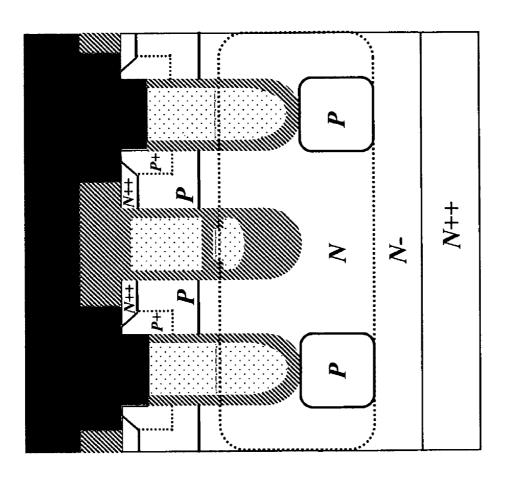

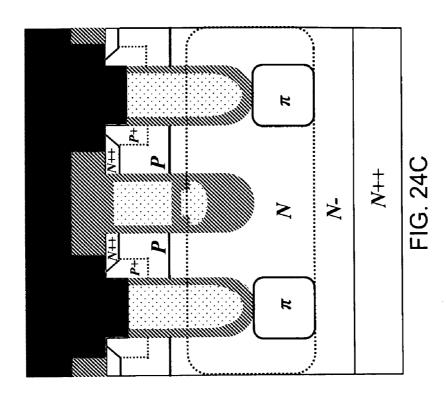

A basic cell of an n-channel MOSFET 30 in accordance with this invention is shown in FIG. 3A. MOSFET 30 is formed in a semiconductor die comprising an n-type epitaxial layer 36 that is grown over a heavily doped n+ substrate 38. 40 MOSFET 30 includes recessed field plate (RFP) trenches 32A and 32B located on either side a gate trench 34 in the n-type epitaxial layer 36. Unlike the trenches in the MOSFET 20 shown in FIG. 2, the thick bottom oxide of the gate trench 34 extends to substantially the same depth as the RFP trenches 32A and 32B. Furthermore, the RFP trenches 32A and 32B and the gate trench 34 are preferably formed in the same processing step and therefore are self-aligned (i.e., the RFP trenches 32A and 32B are equally spaced from gate trench 34 regardless of processing and alignment variations), 50 and RFP trenches 32A and 32B and gate trench 34 are of equal or substantially equal depth (e.g., the respective depths of RFP trenches 32A and 32B are within +/-10%, or preferably  $\pm -5\%$ , of the depth of gate trench 32). The mesas between the trenches contain n+ source regions 37 and 55 p-body regions 39, and below p-body regions 39 is an n-type drain-drift region 41 of epitaxial layer 36. The drain-drift region 41 includes areas 41A between RFP trenches 32A and 32B and gate trench 34. The drain-drift region 41 and the n+ substrate 38 together form the drain 43 of MOSFET 30.

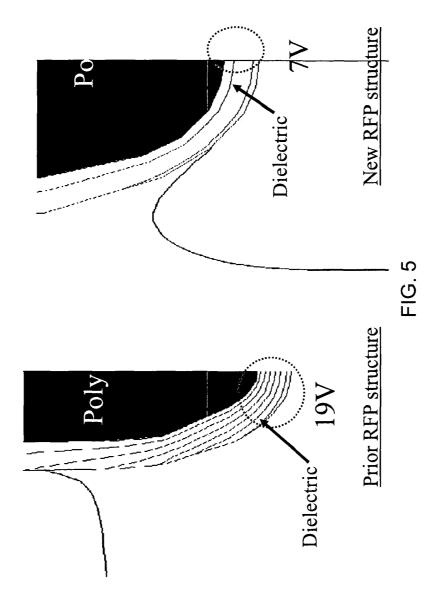

In the prior art MOSFET 20 shown in FIG. 2, when the body-drain junction is reverse-biased, the electric field strength is reduced and hence the breakdown voltage is increased due to the spread of the depletion region between the two deep trenches 22, mainly in the drift region below the 65 gate trench 24. In MOSFET 30, under the same conditions the electric field is further reduced because the depletion layer is

4

initially limited to the narrower areas 41A of drain-drift region 41 located between the thick oxide of the gate trench 34 and RFP trenches 32A and 32B. Moreover, since the trenches 22 in the prior art MOSFET 20 are deeper than the gate trench 24, the electric field at the bottom of trenches 22 is higher, which sets a lower limit on the thickness of the oxide layer in trenches 22. This limitation degrades the effectiveness of the trenches 22 in reducing the electric field in the channel of MOSFET 20.

Referring again to FIG. 3A, the walls of trenches 32A and 32B are lined with a layer 33 of an insulating material such as silicon dioxide (SiO<sub>2</sub>) and trenches 32A and 32B contain RFP electrodes 35, each of which comprises a layer of a conductive material such as n-type or p-type doped polysilicon. The oxide layer 33 preferably has a breakdown voltage that exceeds the breakdown voltage of MOSFET 30. The gate trench 34 is filled with a layer 40 of insulating material up to the level of the p-n junctions between p-body regions 39 and the drain-drift region 41 of epitaxial layer 36. Above insulating layer 40 is a gate electrode 42, which may be formed of n-type doped polysilicon and which is separated from epitaxial layer 36 by a gate dielectric layer 44. Channel regions 45 (represented by the dashed lines) lie within the p-body regions 39 adjacent the gate dielectric layer 44. The thickness of insulating layer 40 is preferably set so as to minimize the overlap of the gate electrode 42 and the drain-drift region 41. An overlying source contact layer 46 contacts n+ source regions 37, and a drain contact layer 31 contacts n+ substrate 38. Contact layers 46 and 31 are typically formed of a metal although they could also be formed of another conductive

The RFP electrodes 35 in RFP trenches 32A and 32B extend to a level that is deeper below the surface 36A of epitaxial layer 36 than the bottom of gate electrode 42. RFP 35 electrodes 35 may be independently biased or, as shown in FIG. 3B, may be connected to n+ source regions 37 outside the plane of the drawing.

In some embodiments, the doping concentration of the drain-drift region 41 in the areas between the RFP trenches 32A and 32B and the gate trench 34 is less (e.g., 5×10<sup>15</sup> to 1.5×10<sup>16</sup> cm<sup>-3</sup>) than the doping concentration of the drain-drift region 41 in the area below the gate trench 34 (e.g., 2×10<sup>16</sup> to 3×10<sup>16</sup> cm<sup>-3</sup>). This structure improves depletion-spreading in the areas of drain-drift region 41A between the RFP trenches 32A and 32B and the gate trench 34 when the PN junction between the body region 39 and the drain-drift region 41 is reverse-biased due to the limited depletion charge in region 41A. This can be further improved, for example, by varying the doping of epitaxial layer 36 as it is being formed. It also results in shorter channel length, which in turn provides a lower Ron, a lower gate-to-source capacitance (Cgs), and a lower gate-to-drain capacitance (Cgd)

In the embodiments shown in FIGS. 3A and 3B, n+ source regions 37 extend between the gate trench 34 and the RFP trenches 32A and 32B. Alternatively, a MOSFET 50, shown in the top view of FIG. 4A and the cross-sectional view of FIG. 4B, is similar to MOSFET 30, but in selected areas the n+ source regions 37 are replaced by p+ body contact regions 52 so as to avoid snap-back or second breakdown characteristics. In FIG. 4A, the view at cross-section 3A-3A is identical to cross-sectional view shown in FIG. 3A, and the view at cross-section 4B-4B is shown in FIG. 4B.

When a conventional N-channel MOSFET operates in the third quadrant, its drain is negatively biased with respect to its source-body electrode, and the diffusion current results in minority carrier injection and a high Qrr. In MOSFETs 30 and 50, because the n+ source regions 37 extend all the way across

### US 7,843,004 B2

5

the mesa between the gate trench 34 and the RFP trenches 32A and 32B, the RFP electrodes 35 provide a majority carrier channel current path from drain to source in addition to that provided by the gate electrode in the conventional structure. The combined effect of the RFP and gate electrodes results in a significant reduction in the minority carrier diffusion current and reverse recovery charge Qrr than in conventional structures. In other words, in the third quadrant operation the RFP electrode acts as an additional gate without the penalty of the added gate-drain capacitance (Cgd) and gatesource capacitance (Cgs).

The RFP electrodes 35 also function as a recessed field plates to reduce the electric field in the channel regions 45 when MOSFETs 30 and 50 are reverse-biased. This effect enables the use of shorter channel lengths, without concern 1 about punchthrough breakdown, and this results in a lower specific on-resistance (Ron\*A) and a lower gate charge (Qg). Unlike MOSFET 20, the drift regions 41A below p- body regions 39 are constrained between the thick gate bottom oxide and the RFP electrode and are therefore more effec- 20 tively depleted. Therefore, a deeper depletion layer results for the same reverse bias body-drain junction conditions, and a shorter channel can be used, resulting in a lower on-resistance. Furthermore, because the gate-to-drain capacitance (Cgd) drops at a faster rate with applied drain-source voltage 25 Vds, a lower gate-drain charge Qgd and a better Ron-Qgd trade-off are realized. In other words, the combined effect of the RFP electrodes 35 and of having the gate trench 34 filled with insulating layer 40 up to the junctions between the p-body regions 39 and the drain-drift region 41 helps to 30 deplete area of the drain-drift region 36 between the trenches 32A, 32B and 34 at a higher rate as the drain-source voltage Vds is increased while MOSFETs 30 and 50 are in the offstate. Therefore, a lower gate-drain charge (Qgd) results because of the low gate-to-drain capacitance (Cgd) and its 35 fast falling rate with increasing Vds. Furthermore, the doping in the p-body regions 39 can be adjusted to obtain a lower threshold voltage at the same breakdown or punchthrough voltage. The doping in the p-body regions 39 can be further adjusted so that the p-body regions 39 are fully depleted, 40 which significantly reduces gate charge Qg.

In MOSFET 30 shown in FIGS. 3A and 3B, the RFP electrodes 35 are separated from the source contact layer 46 by an insulating layer 48. Alternatively, in a MOSFET 60, shown in FIGS. 5A and 5B, there is no insulating layer 48, and 45 RFP electrodes 62 in RFP trenches 64A and 64B extend upward to electrically contact the source contact layer 46. FIG. 5A is a view taken at a cross-section corresponding to cross-section 3A-3A in FIG. 4A; FIG. 5B is a view taken at a cross-section corresponding to cross-section 4B-4B in FIG. 50

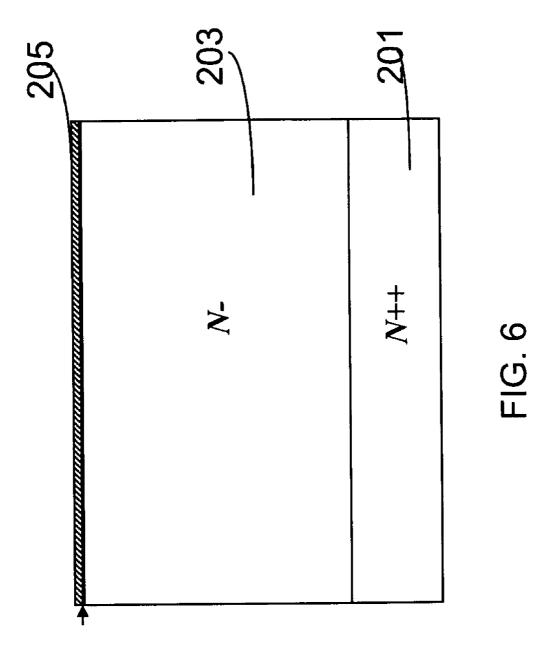

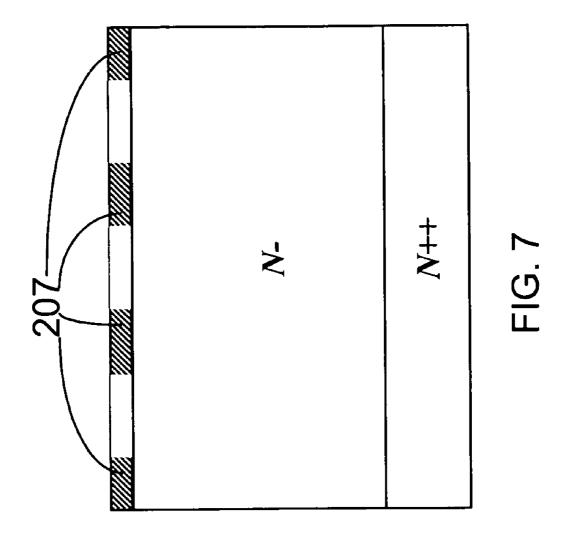

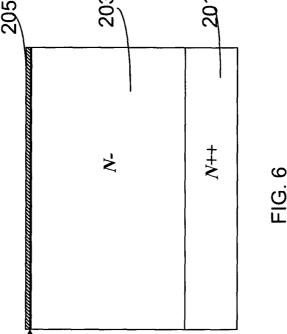

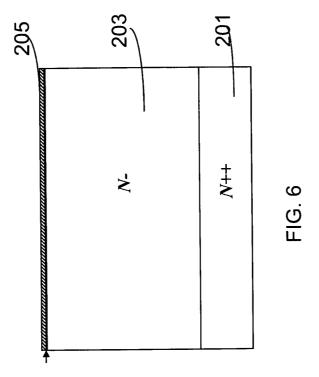

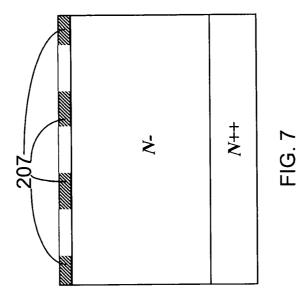

An exemplary process for fabricating MOSFET 30 of FIG. 3A is shown in FIGS. 6A-6H. As shown in FIG. 6A, the starting material is the heavily-doped n+ substrate 38, which may be doped, for example, with phosphorus or arsenic. The 55 n-type epitaxial layer 36 is grown on top of the n+ substrate 38. A thin oxide layer 72 is grown over the n-type epitaxial layer 36, and a silicon nitride layer 74 is deposited on top of the oxide layer 72. For example, the oxide layer 72 can be 200-300 A thick, and the silicon nitride layer 74 can be 1000 60 A thick.

A photoresist mask (not shown) is used to pattern the silicon nitride layer **74** and oxide layer **72** with openings **76**, as shown in FIG. **6**B.

The epitaxial layer 36 is etched through the openings 76 to 65 form the RFP trenches 32A and 32B and the gate trench 34, as shown in FIG. 6C. It will be understood that trenches 32A,

6

32B and 34 are illustrative only; typically numerous trenches would be formed. A thin thermal oxide layer (not shown), for example, 300 A thick, is grown on the walls of trenches 32A, 32B and 34, and trenches 32A, 32B and 34 are then filled with a layer 78 of deposited silicon dioxide such as LTO or TEOS or high density plasma (HDP) oxide. The resulting structure is shown in FIG. 6C.

The oxide layer 78 is etched back using a dry plasma etch or chemical-mechanical polishing (CMP) technique to a level the same as or slightly below the top surface of the silicon nitride layer 74. A photoresist mask layer 80 is deposited and patterned to form openings 82 over the RFP trenches 32A and 32B, as shown in FIG. 6D, and the oxide layer 78 in the RFP trenches 32A and 32B is then completely or partially etched through the openings 82 by a wet or a dry plasma etch or a combination of wet and dry etching to yield the structure shown in FIG. 6D. Silicon nitride layer 74 prevents epitaxial layer 36 from being etched.

The photoresist mask layer 80 is removed and the portion of oxide layer 78 remaining in the gate trench 34 is partially etched by wet etching. At the same time, the remaining portion of oxide layer 78 at the bottom of the RFP trenches 32A and 32B is removed. This is followed by an etch to remove the silicon nitride layer 74 and a wet oxide etch to remove the oxide layer 72 and any remaining oxide on the walls of the RFP trenches 32A and 32B. The resulting structure is shown in FIG. 6E.

As shown in FIG. 6F, a thermal process is then performed to form oxide layer 33 on the walls of the RFP trenches 32A and 32B and gate dielectric layer 44 on the walls of the gate trench 34 above the remaining portion of the oxide layer 78 (which forms the insulating layer 40 at the bottom of the gate trench 34). This process also creates an oxide layer 80 on the top surface of the epitaxial layer 36. These oxide layers could have a thickness, for example, in the range of 200 A to 1000 A. A layer 82 of polysilicon is then deposited and then doped, for example, by implanting with an n-type dopant such as phosphorus and then etched back to a level at or below that of the surface of oxide layer 80 by a plasma dry etching or CMP technique. Several masking and implant steps are performed to form the p-body regions 39 and p+ body contact regions 52 (shown in FIGS. 4A and 4B), using a p-type dopant such as boron, and to form the n+ source regions 37, using an n-type dopant such as arsenic or phosphorus or a combination thereof. A deep p layer (not shown) may also be implanted at this step or earlier in the process.

The polysilicon layer 82 is etched back and an oxide layer is deposited and later etched, leaving the RFP electrodes 35 and the gate electrode 42 covered by an oxide layer 84, as shown in FIG. 6G

The source contact layer 46 is deposited and defined by a photoresist mask (not shown). The back side of the n+ substrate 38 is thinned and the drain metal layer 31 deposited, resulting in the MOSFET 30 shown in FIGS. 3A and 6H.

In an alternative method, after the step shown in FIG. 6D the portions of oxide layer 78 remaining in RFP trenches 32A and 32B and in gate trench 34 are etched, and the steps shown in FIGS. 7A and 7B are performed. As shown in FIG. 7A, with oxide layer 72 and nitride layer 74 still in place oxide layers 33 and 44 are thermally grown on the walls of the RFP and gate trenches 32A/32B and 34, respectively. A polysilicon layer 85 is deposited and partially removed by etching or CMP so that the surface of the polysilicon layer 85 is level with or below the surface of the nitride layer 74. The resulting structure is shown in FIG. 7A.

The polysilicon layer 85 is etched (e.g., by about  $0.1 \mu m$ ) and an oxide layer 87 is deposited and etched back so that the

### US 7,843,004 B2

surface of oxide layer **87** is level with or below the nitride layer **74**. Nitride layer **74** is removed by etching and optionally oxide layer **72** may be removed and a sacrificial oxide layer (not shown) may be re-grown. P-body regions **39** and n+source regions **37** are implanted. Oxide layer **87** is then removed from the areas over the n+source regions **37**, leaving the structure shown in FIG. **7B**. A source contact layer (not shown) is then deposited on top of the oxide layer **87** and n+

source regions 37.

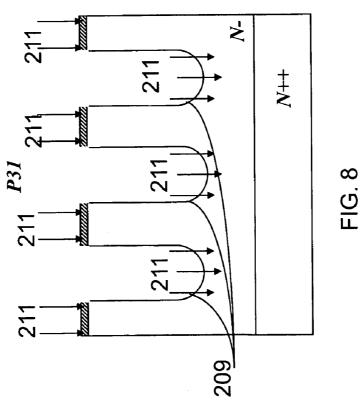

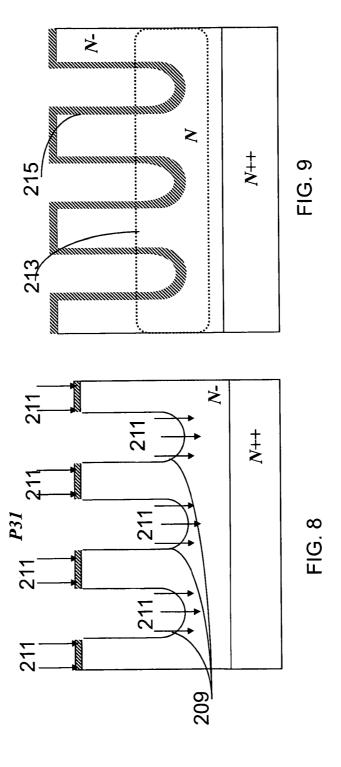

Numerous variations of the MOSFETs described above are 10 within the scope of this invention. In a MOSFET 70 shown in FIG. 8A, an insulating layer 92 over the gate electrode 42 extends above the surface 36A of epitaxial layer 36 and partially covers the n+ source regions 37, while the RFP electrodes 35 remain recessed below the surface 36A. A source 15 contact layer 94 contacts the RFP electrodes 35 so that the RFP electrodes 35 are biased at the source potential. FIG. 8B is another view of MOSFET 70, taken at a cross-section similar to cross-section 4B-4B shown in FIG. 4A, where the n+ source regions are replaced by p+ body contact regions 52.

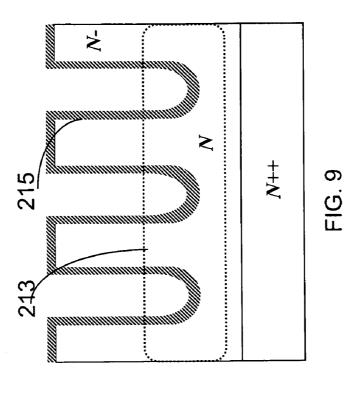

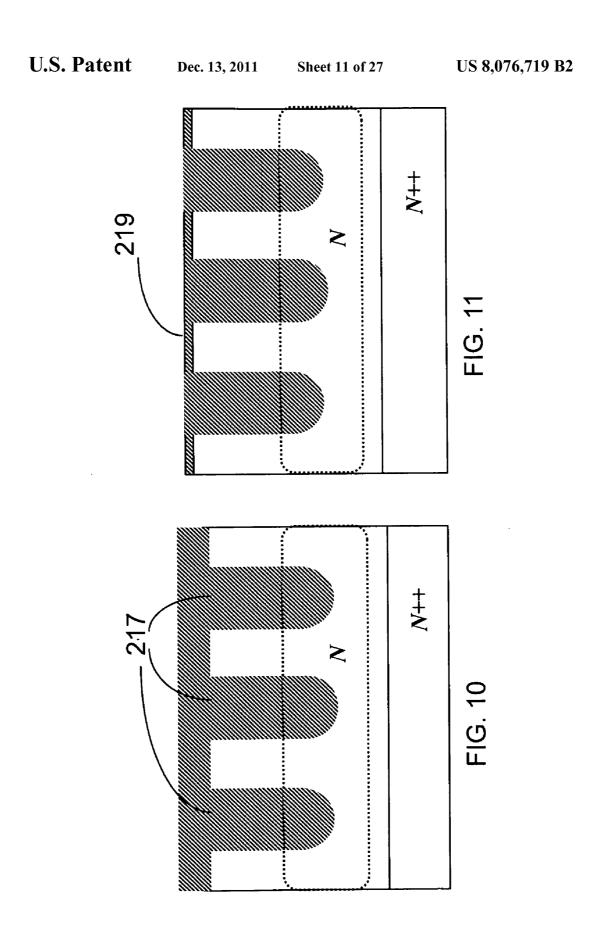

A MOSFET 80, shown in FIG. 9, is similar to MOSFET 70 except that p+ body contact regions 96 are formed adjacent to n+ source regions 98 at the surface 36A of epitaxial layer 36 to provide a source-body short via source contact layer 94. In MOSFET 80, it would not be necessary to interrupt the n+ 25 source regions with p+ body contact regions 52 as shown in FIG. 4A to provide a source-body short. MOSFET 90, shown in FIG. 10, is similar to MOSFET 80 except that p+ body contact regions 99 extend to a level below the bottoms of n+ source regions to provide a larger surface along the walls of 30 RFP trenches 32A and 32B for contact with source contact layer 94. A process for making MOSFET 90 is shown in FIGS. 14A-14H.

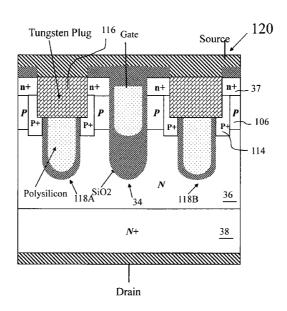

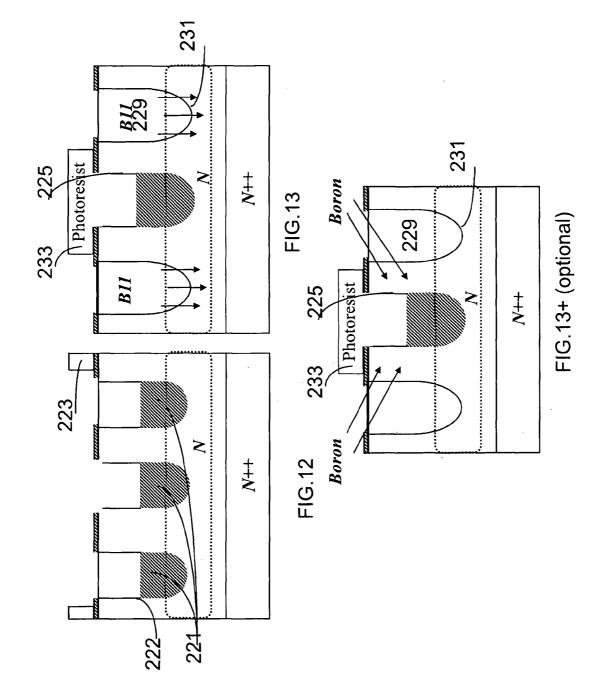

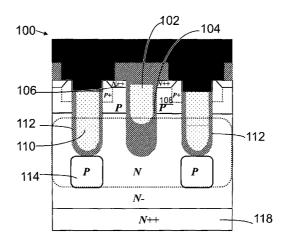

In MOSFET 100, shown in FIG. 11, p+ body contact regions 104 are formed below the n+ source regions 37 and 35 adjacent to the p-body regions 106. The bottom junctions of p-body regions 106 and p+ body contact regions 104 are at approximately the same level in epitaxial layer 36. In RFP trenches 102A and 102B, the RFP electrodes 112 and the oxide layers 110 are recessed sufficiently to permit the source 40 contact layer 108 to contact the p+ body contact regions 104, thereby providing a source-body short. In the gate trench 34, insulating layer 92 extends above the surface 36A of epitaxial layer 36 and covers the n+ source regions 37. MOSFET 100 may allow for a higher cell density and therefore a lower 45 specific on-resistance. MOSFET 110, shown in FIG. 12, is similar to MOSFET 100 except that p+ body contact regions 114 extend to a level below the bottom of p-body regions 106. MOSFET 120, shown in FIG. 13, is similar to MOSFET 110 except that RFP trenches 118A and 118 B contain metal plugs 116, comprising for example tungsten, which contact both the source regions 37 and the p+ body contact regions 114 to provide a very low-resistance conduction path between source regions 37 and p+ body contact regions 114

FIGS. 14A-14H illustrate a process of fabricating MOS-FET 90, shown in FIG. 10. The process starts with growing n-type epitaxial layer 36 on top of n+ substrate 38. As shown in FIG. 14A, an oxide layer 120 (e.g., 0.5 µm thick) and a photoresist trench mask layer 122 are deposited over the top surface of epitaxial layer 36. Mask layer 122 is patterned to form openings and oxide layer 120 and epitaxial layer 36 are etched through the openings to form RFP trenches 32A and 32B and gate trench 34. The mask layer 122 and oxide layer 120 are removed, and a sacrificial oxide layer and a pad oxide layer (not shown) are grown.

As shown in FIG. 14B, an oxide layer 124 is deposited in trenches 32A, 32B and 34. Oxide layer 124 is preferably a

high quality oxide, such as a high-density plasma oxide. An active mask (not shown) is deposited and patterned with an opening over the active areas of the die, and oxide layer 124 is etched down into trenches 32A, 32B and 34, as shown in FIG. 14C. The active mask prevents optional field termination oxide (not shown) or oxide layer 124 from being etched in the

termination areas of the die.

A photoresist bottom oxide (BOX) mask layer 126 is deposited and patterned with openings over the RFP trenches 32A and 32B, and the remains of oxide layer 124 is removed from RFP trenches 32A and 32B, leaving the remains of oxide layer 124 (which becomes insulating layer 40) in the bottom of gate trench 34. The resulting structure is shown in FIG.